# RFCIRCUIT design

A best-seller now thoroughly revised

Two new chapters on RF Front-End Design and RF Design Tools

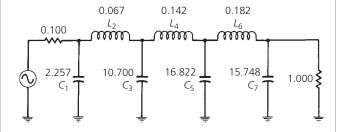

Perfect for the practical, hard-working RF professional

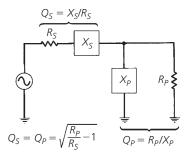

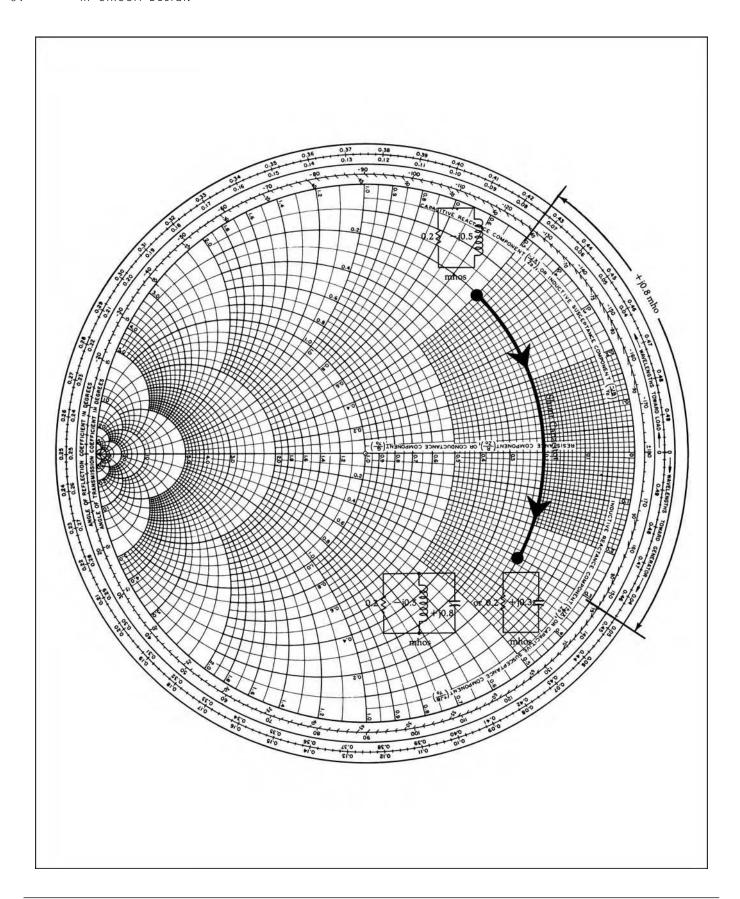

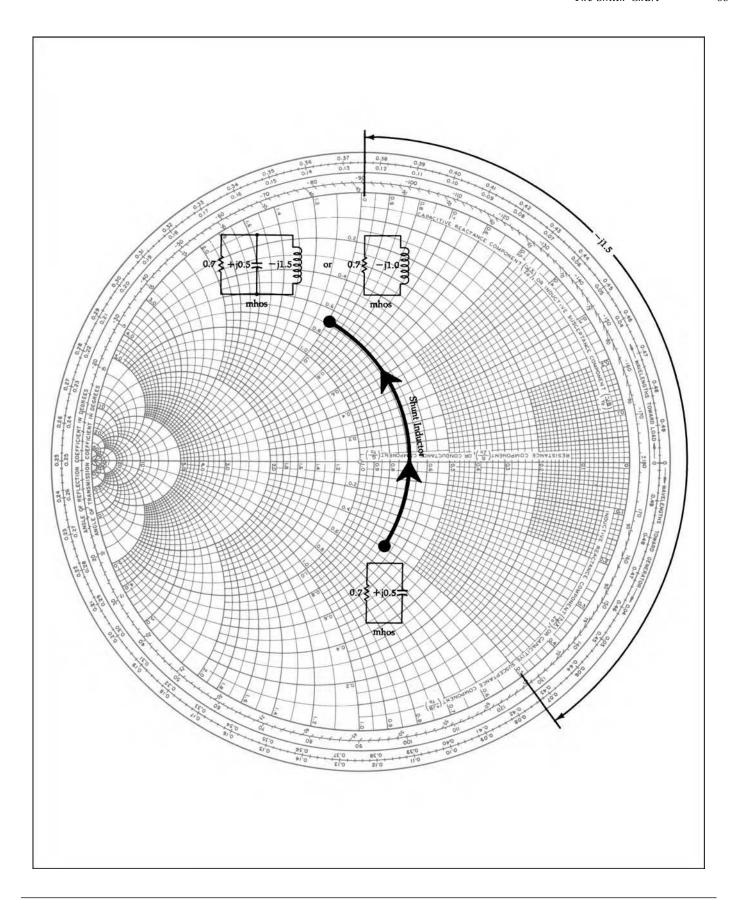

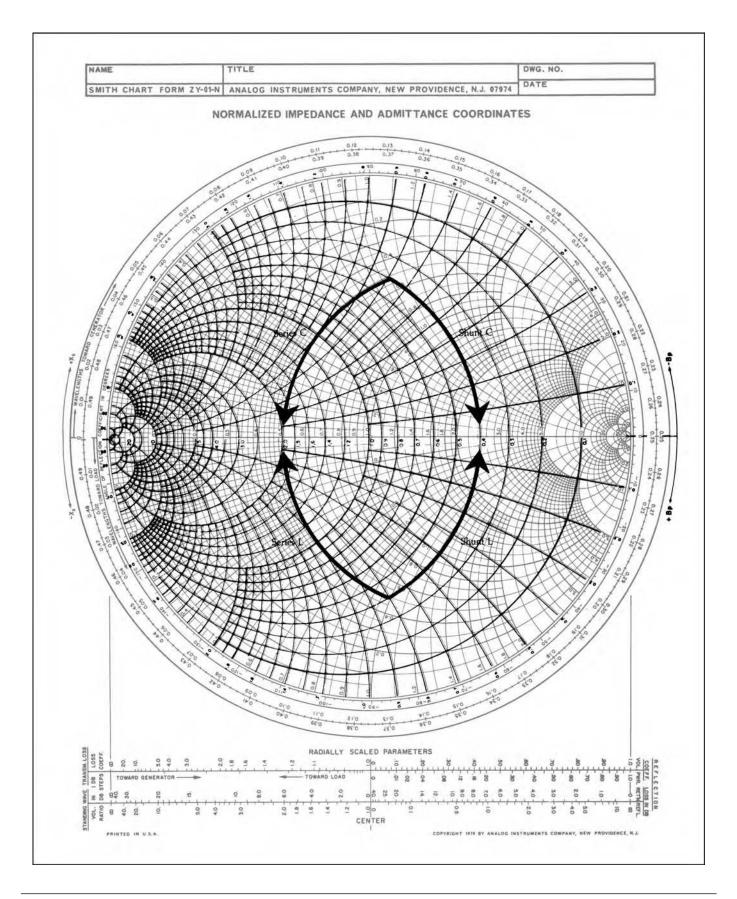

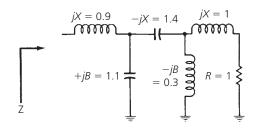

## RF CIRCUIT DESIGN

## RF CIRCUIT DESIGN

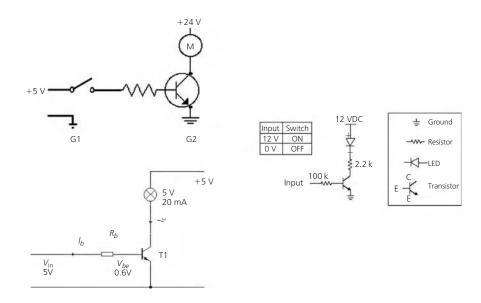

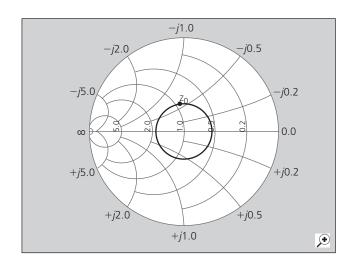

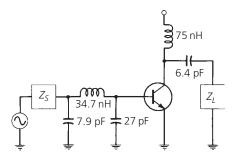

### CHRISTOPHER BOWICK

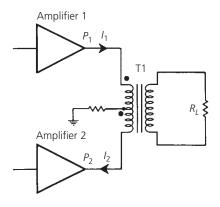

WITH

JOHN BLYLER AND CHERYL AJLUNI

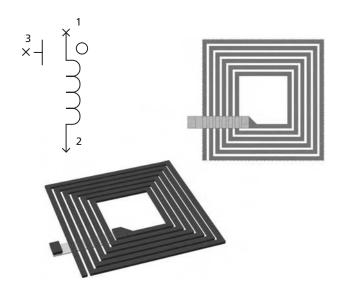

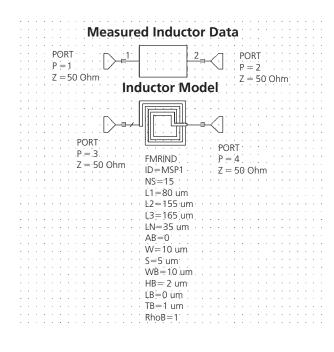

Cover image by iStockphoto

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2008, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: permissions@elsevier.com. You may also complete your request online via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

#### Library of Congress Cataloging-in-Publication Data

Bowick, Chris.

RF circuit design / Christopher Bowick. — 2nd ed.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-7506-8518-4 ISBN-10: 0-7506-8518-2

1. Radio circuits Design and construction. 2. Radio frequency. I. Title.

TK6553.B633 2008 621.384'12—dc22

2007036371

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

ISBN: 978-0-7506-8518-4

For information on all Newnes publications visit our web site at http://books.elsevier.com

Typeset by Charon Tec Ltd (A Macmillan Company), Chennai, India www.charontec.com

Printed in the United States of America

## Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID International

Sabre Foundation

To my children—Isabel and Juan—who have brought me more happiness and grey hairs than I thought possible. Y para mi esposa Rosa, con amor. — JEB

To my husband, Tom, my daughters, Alexis and Emily, and mother, Fran . . . without whose constant cooperation, support and love I never would have found the time or energy to complete this project. — Cheryl Ajluni

## **CONTENTS**

| Preface                                                                                                                                                                                                            | ix  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Acknowledgments                                                                                                                                                                                                    | хi  |

|                                                                                                                                                                                                                    |     |

| CHAPTER 1                                                                                                                                                                                                          | 1   |

| Components and Systems                                                                                                                                                                                             |     |

| Wire – Resistors – Capacitors – Inductors – Toroids – Toroidal Inductor Design – Practical Winding Hints                                                                                                           |     |

| CHAPTER 2                                                                                                                                                                                                          | 23  |

| Resonant Circuits                                                                                                                                                                                                  |     |

| Some Definitions – Resonance (Lossless Components) – Loaded Q – Insertion Loss – Impedance Transformation –                                                                                                        |     |

| Coupling of Resonant Circuits – Summary                                                                                                                                                                            |     |

| CHAPTER 3                                                                                                                                                                                                          | 37  |

| Filter Design                                                                                                                                                                                                      | 37  |

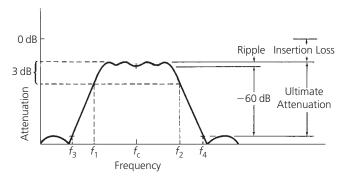

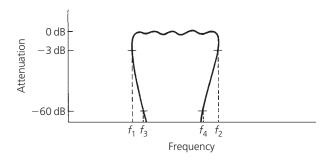

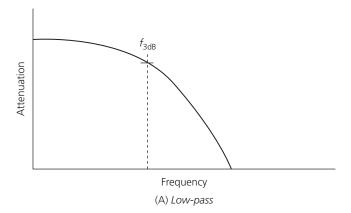

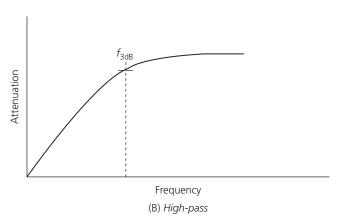

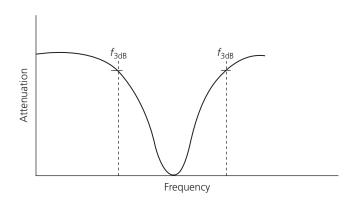

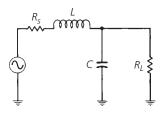

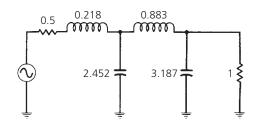

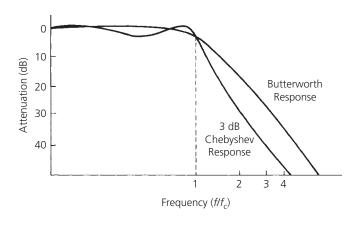

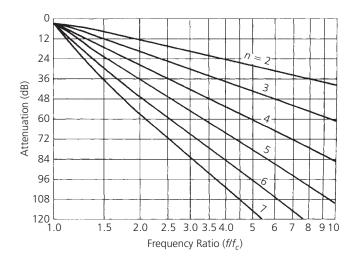

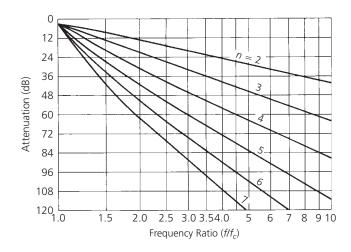

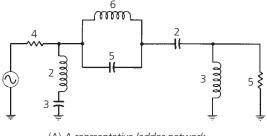

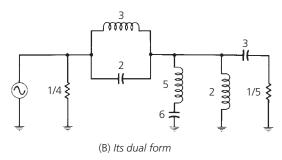

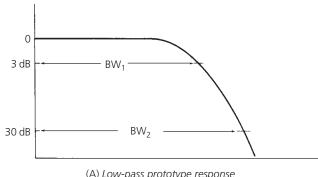

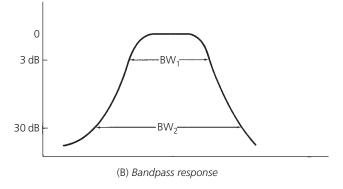

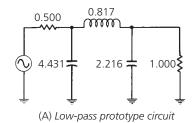

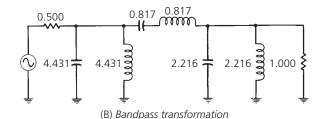

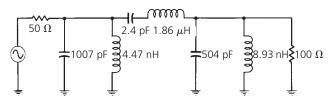

| Background – Modern Filter Design – Normalization and the Low-Pass Prototype – Filter Types – Frequency and                                                                                                        |     |

| Impedance Scaling – High-Pass Filter Design – The Dual Network – Bandpass Filter Design – Summary of the                                                                                                           |     |

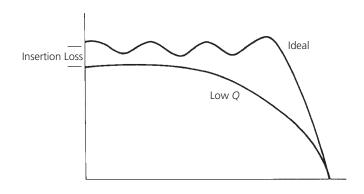

| Bandpass Filter Design Procedure – Band-Rejection Filter Design – The Effects of Finite Q                                                                                                                          |     |

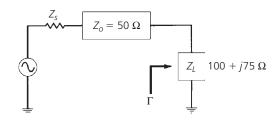

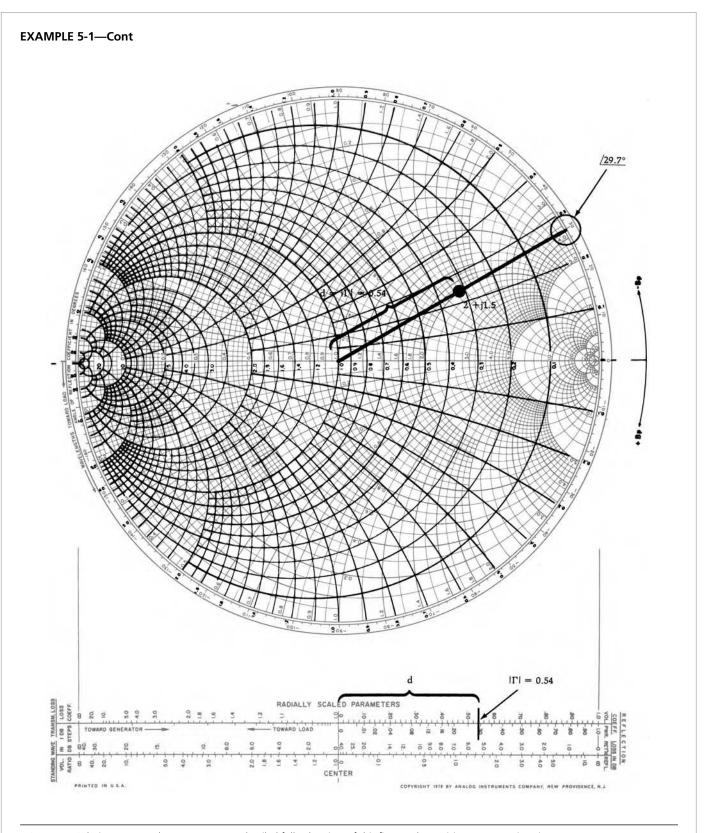

| CHAPTER 4                                                                                                                                                                                                          | 63  |

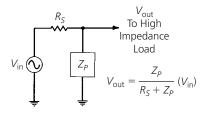

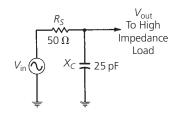

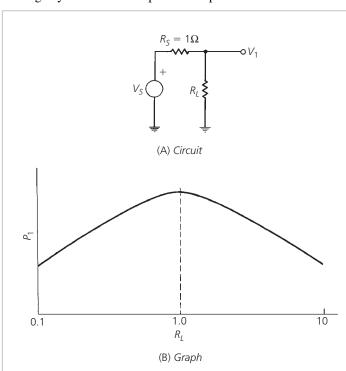

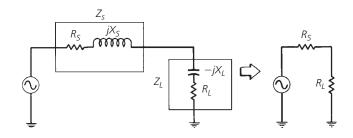

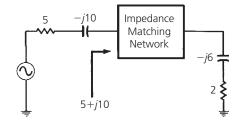

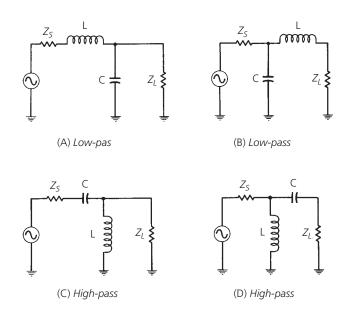

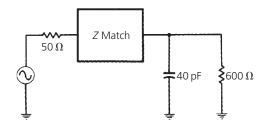

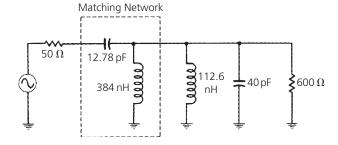

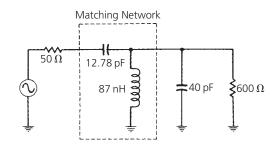

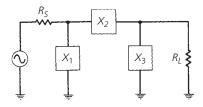

| Impedance Matching  Reductional The Linear Parking With Complex Leads Three Florent Matching Leave Cor Widehard                                                                                                    |     |

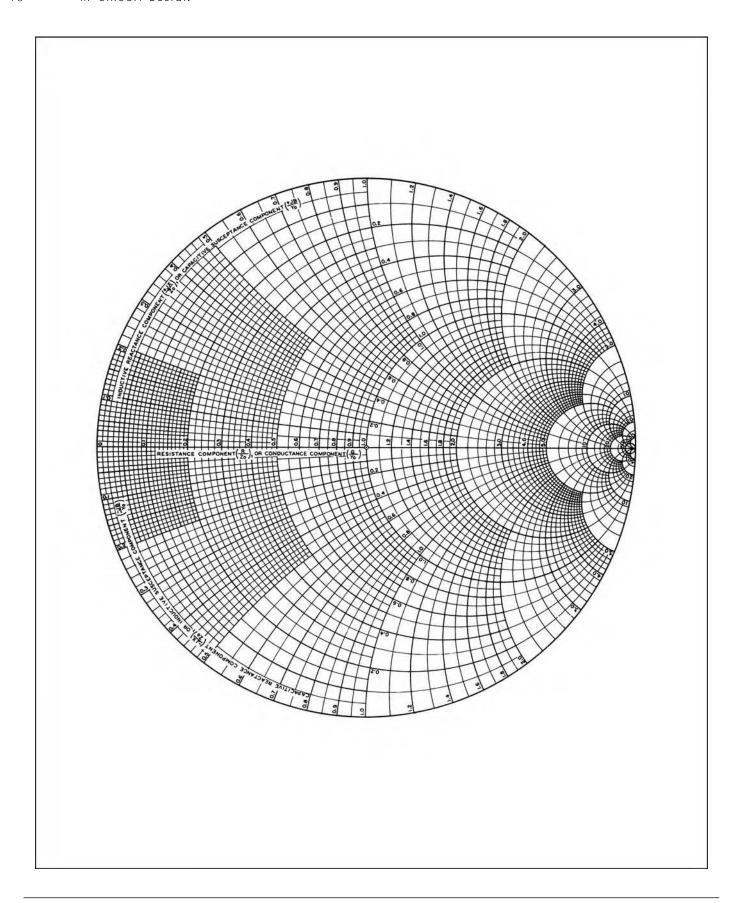

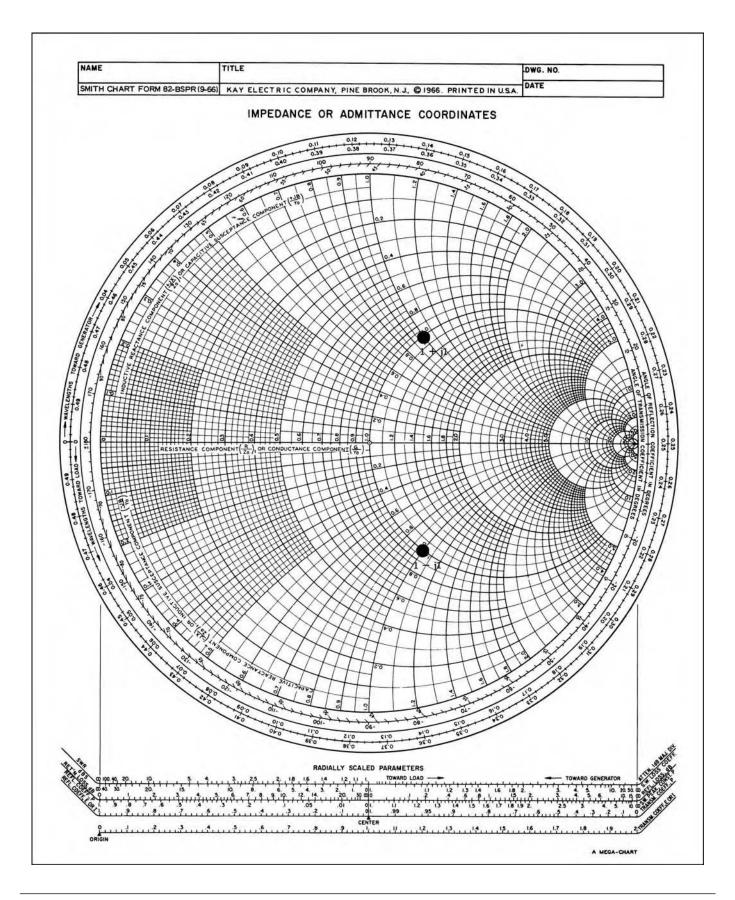

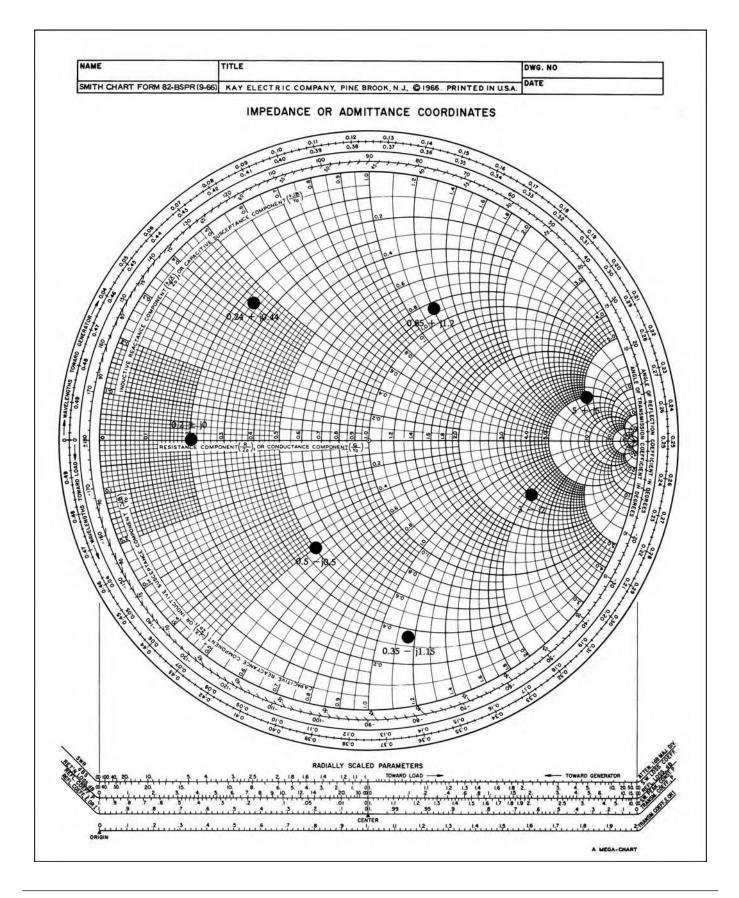

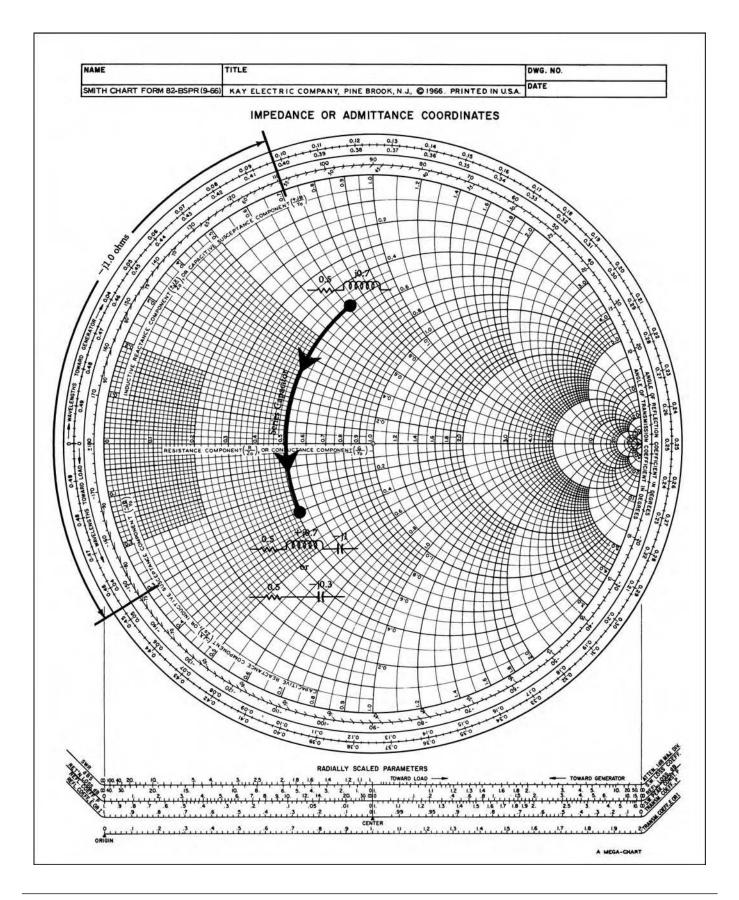

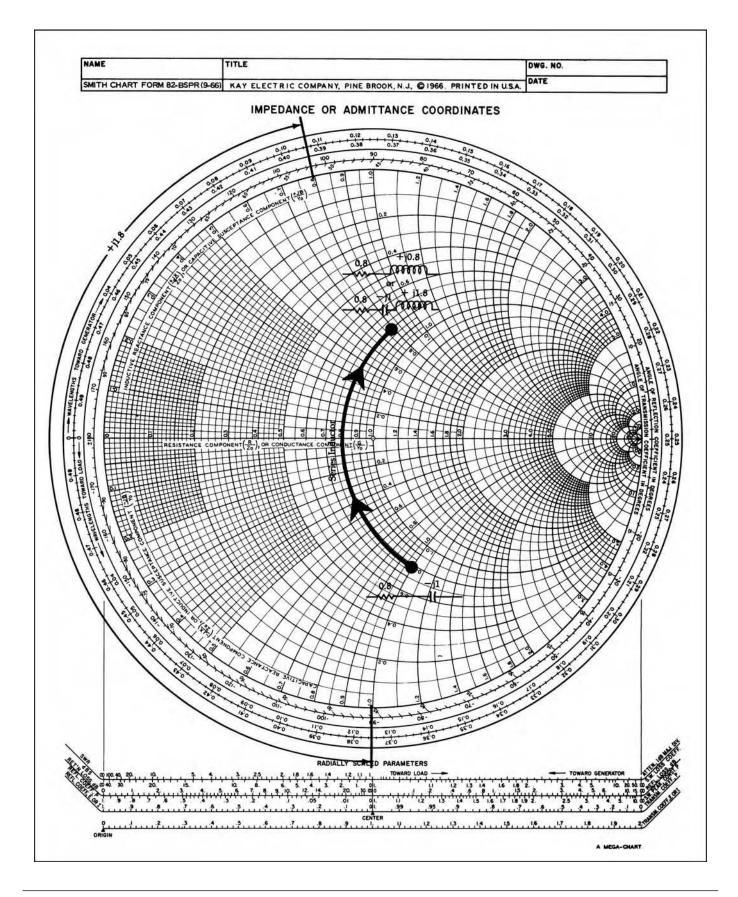

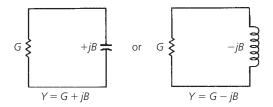

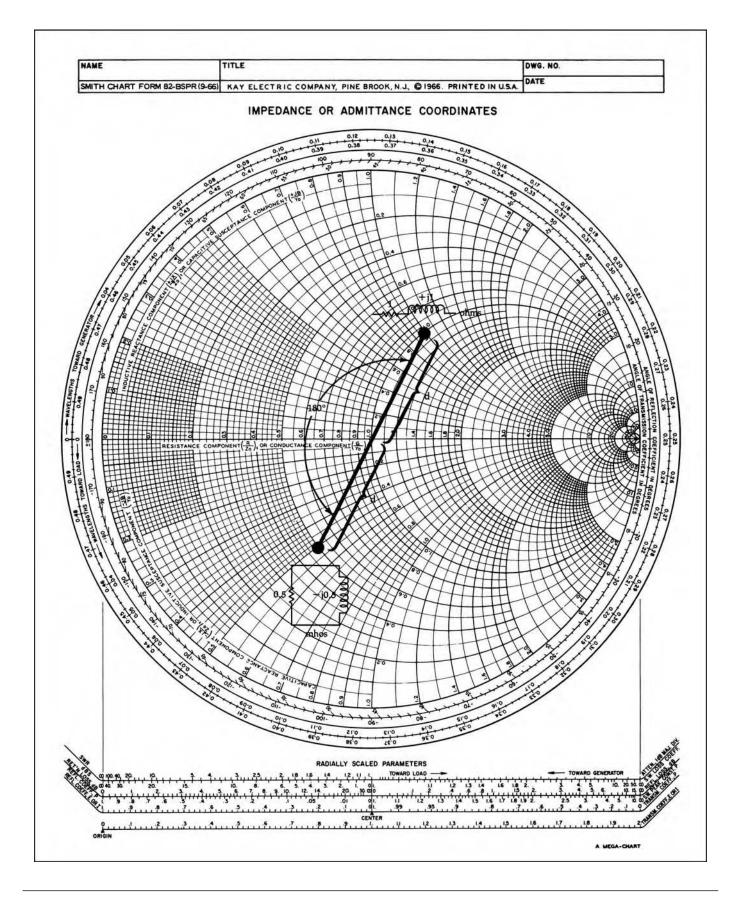

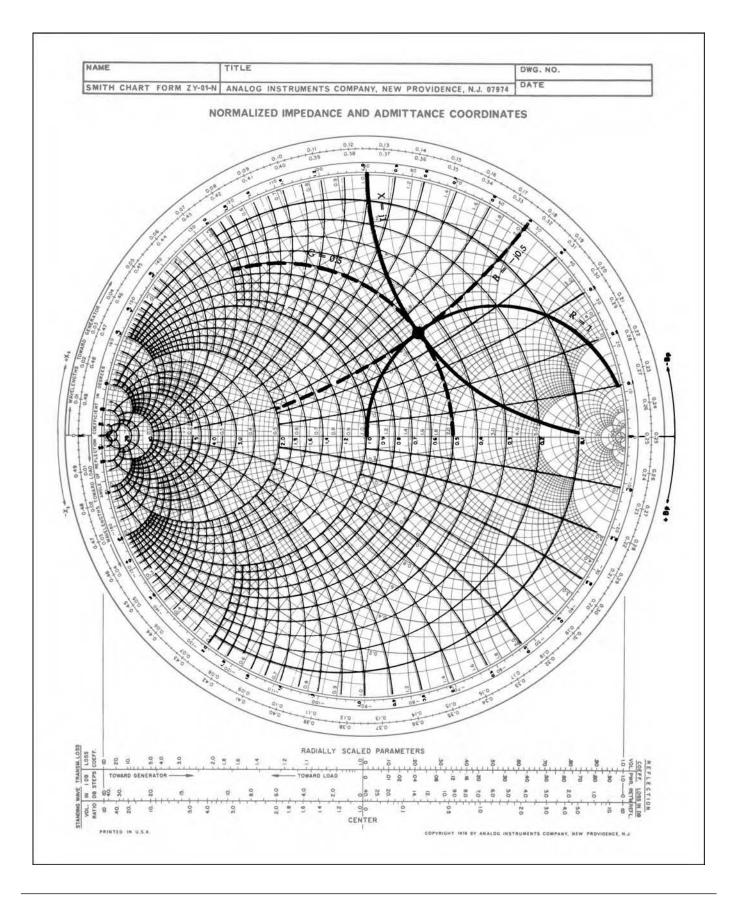

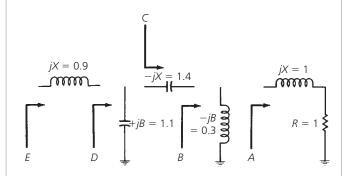

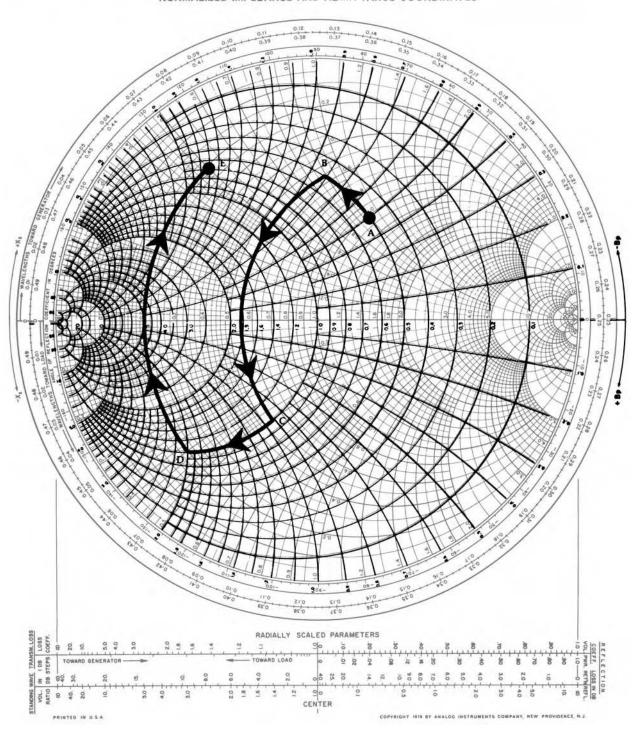

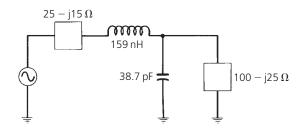

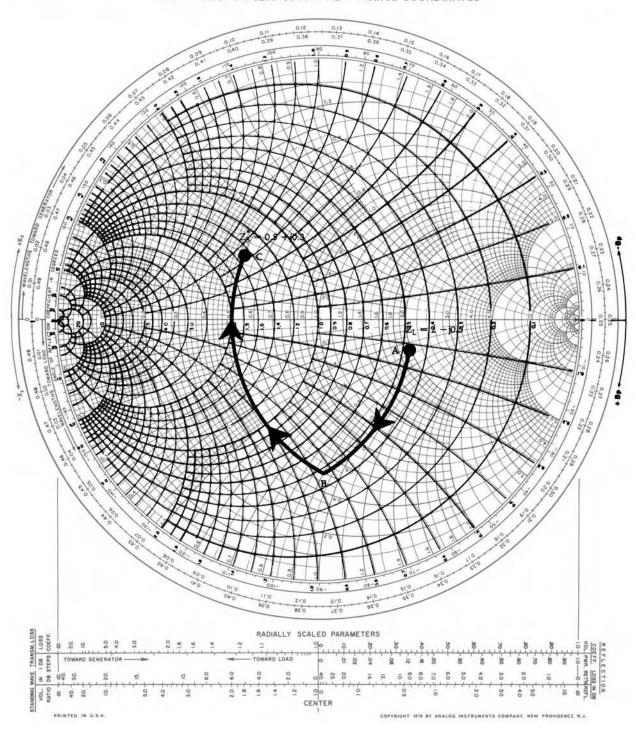

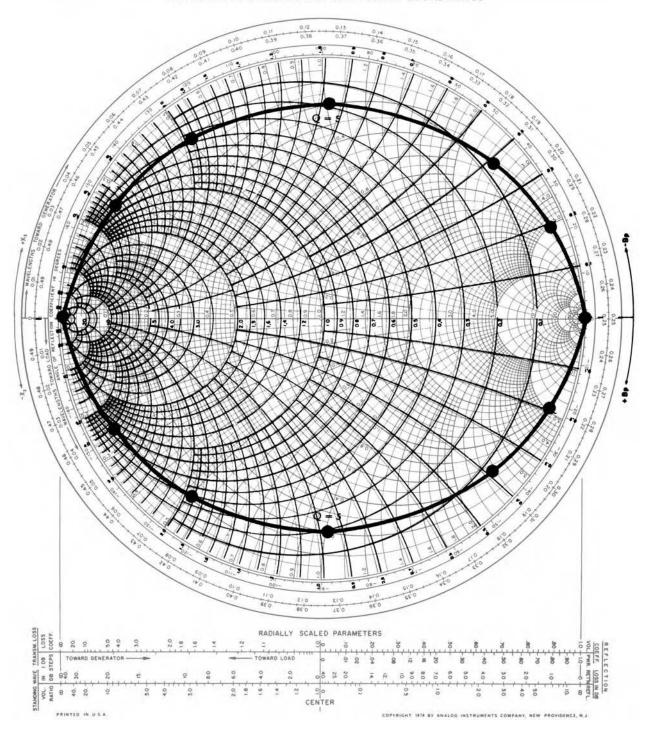

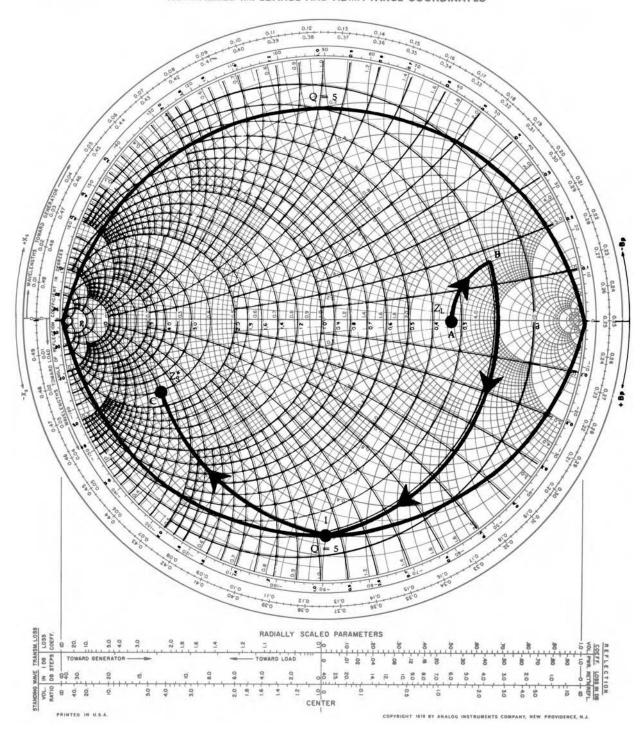

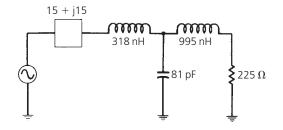

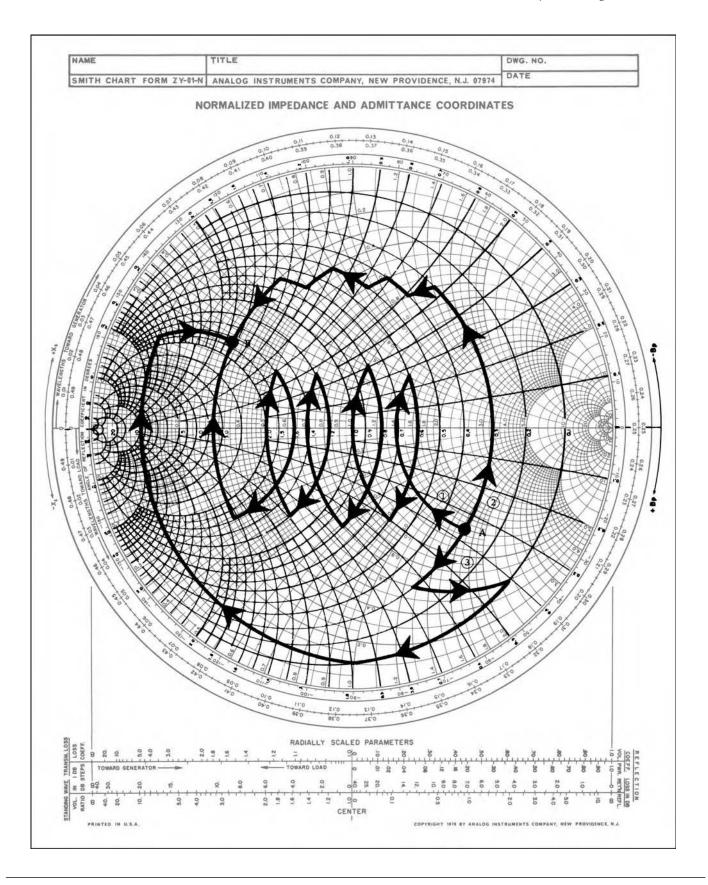

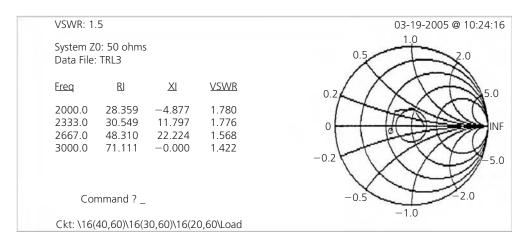

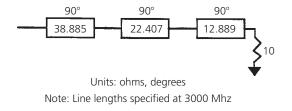

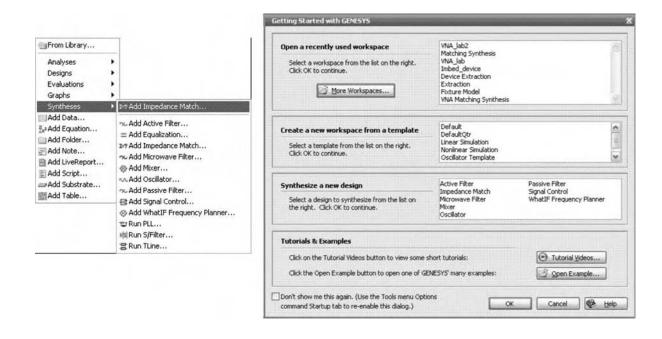

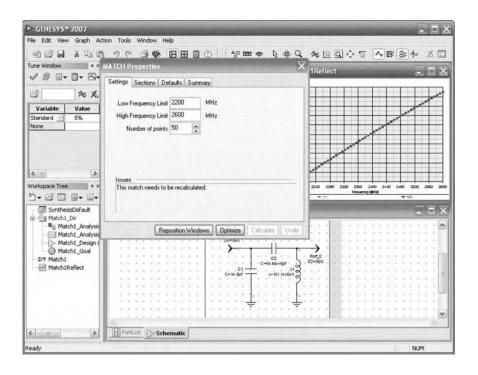

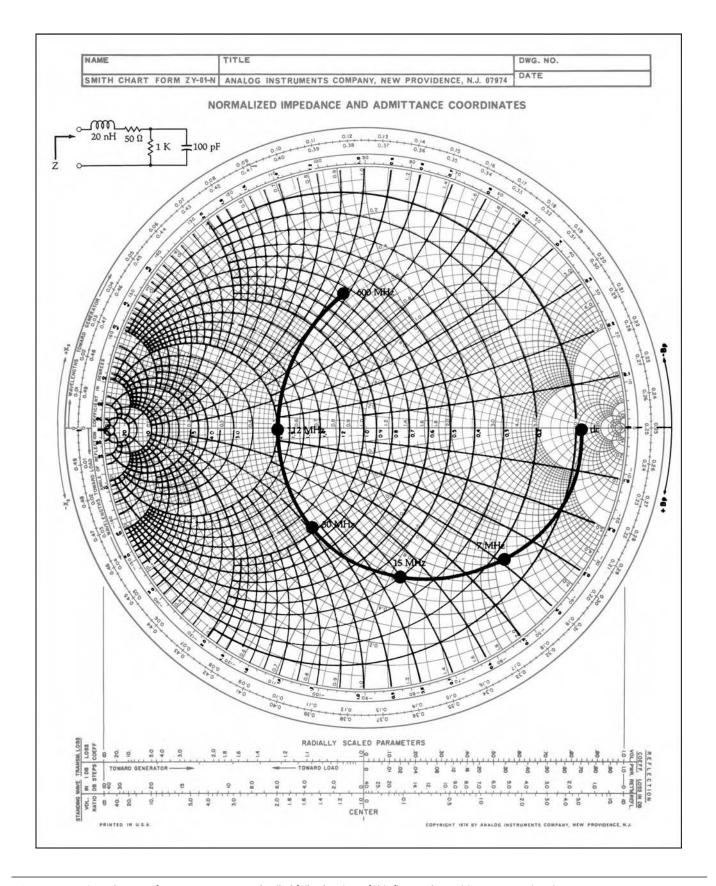

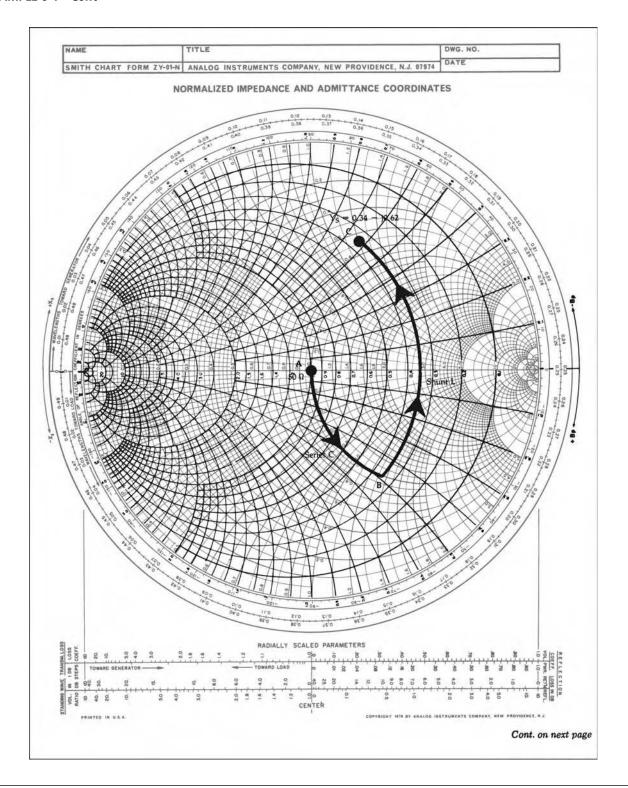

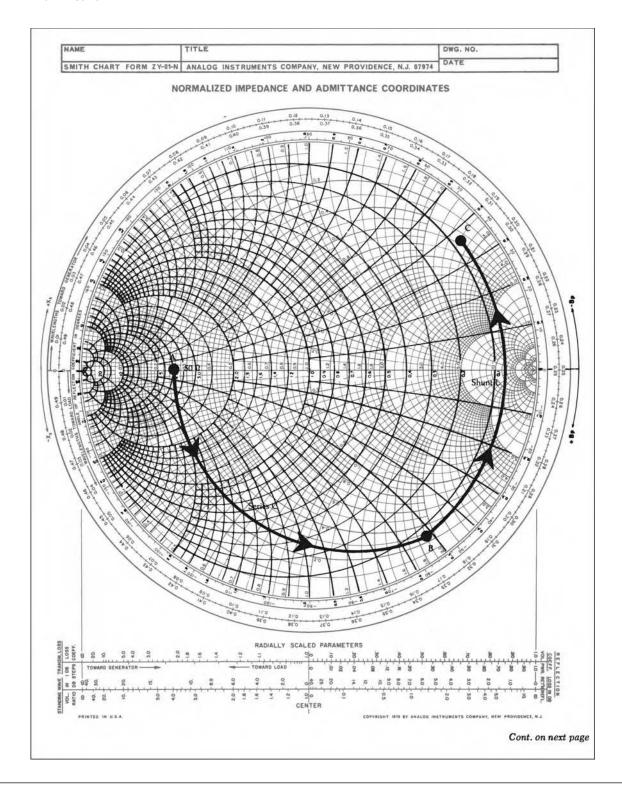

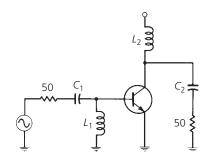

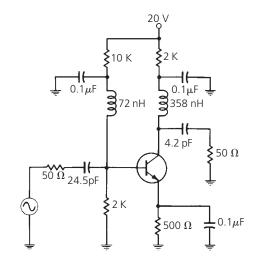

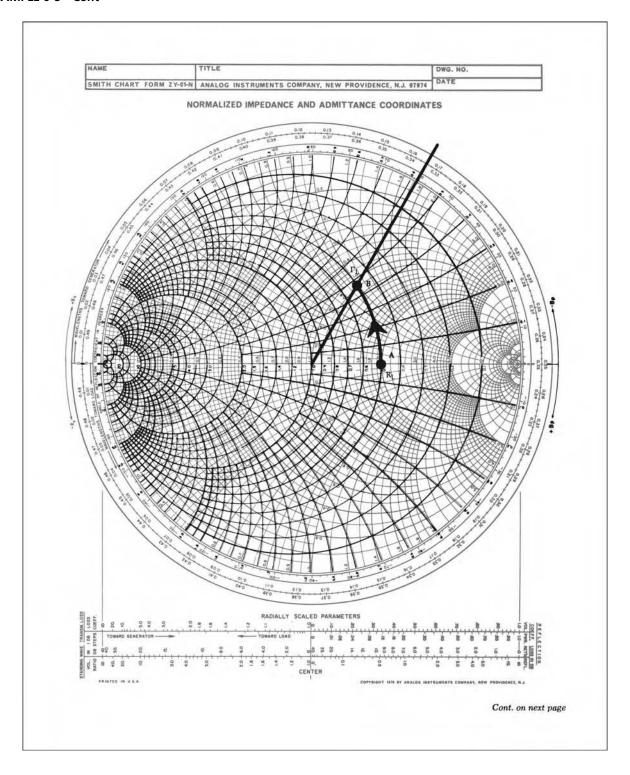

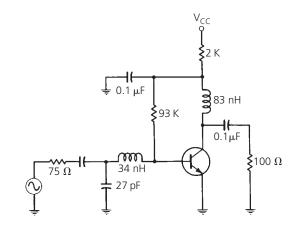

| Background – The L Network – Dealing With Complex Loads – Three-Element Matching – Low-Q or Wideband Matching Networks – The Smith Chart – Impedance Matching on the Smith Chart – Software Design Tools – Summary |     |

|                                                                                                                                                                                                                    | 403 |

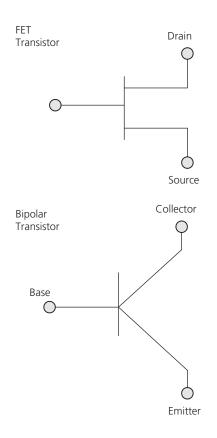

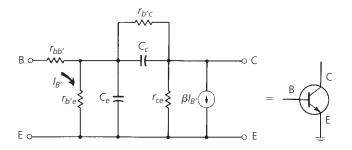

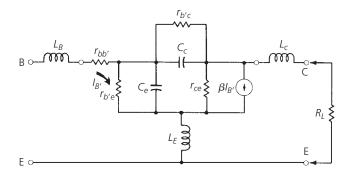

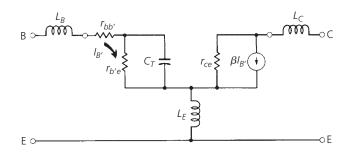

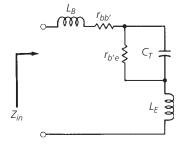

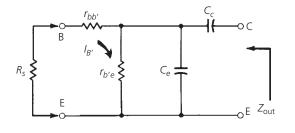

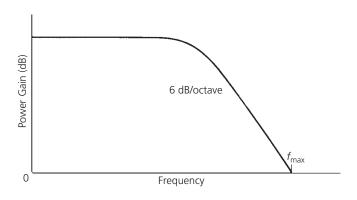

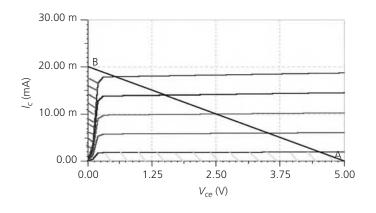

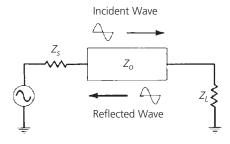

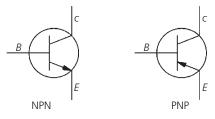

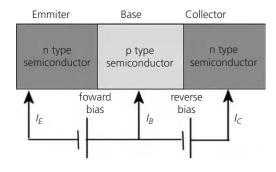

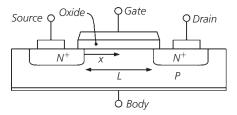

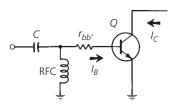

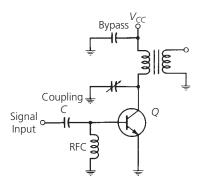

| CHAPTER 5 The Transistor at Radio Frequencies                                                                                                                                                                      | 103 |

| RF Transistor Materials – The Transistor Equivalent Circuit – Y Parameters – S Parameters – Understanding RF                                                                                                       |     |

| Transistor Data Sheets – Summary                                                                                                                                                                                   |     |

| CHAPTER 6                                                                                                                                                                                                          | 125 |

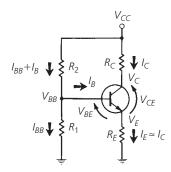

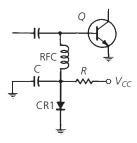

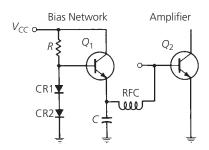

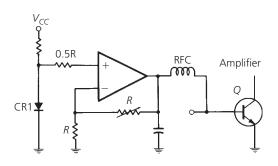

| Small-Signal RF Amplifier Design                                                                                                                                                                                   |     |

| Some Definitions – Transistor Biasing – Design Using Y Parameters – Design Using S Parameters                                                                                                                      |     |

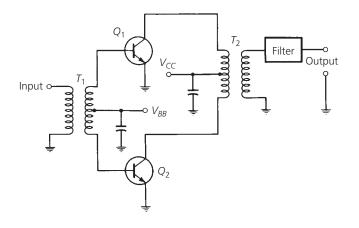

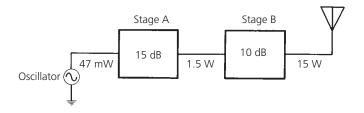

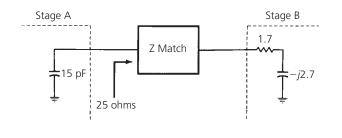

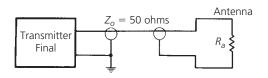

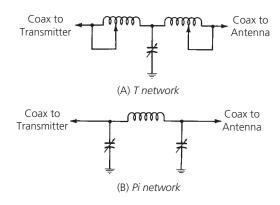

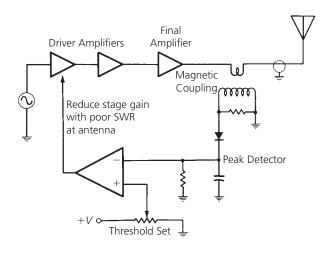

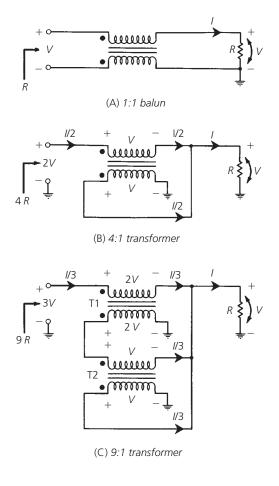

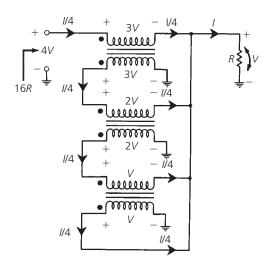

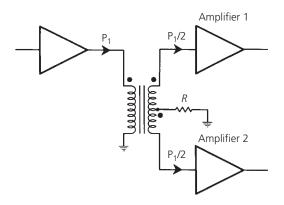

| CHAPTER 7 RF (Large Signal) Power Amplifiers RF Power Transistor Characteristics – Transistor Biasing – RF Semiconductor Devices – Power Amplifier Design – Matching to Coaxial Feedlines – Automatic Shutdown Circuitry – Broadband Transformers – Practical Winding Hints – Summary | 169 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

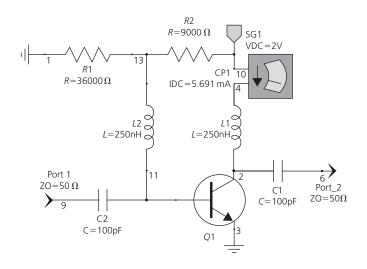

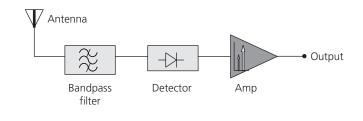

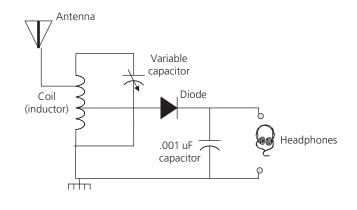

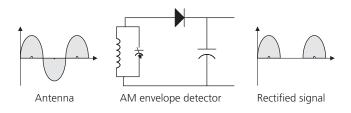

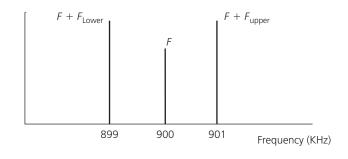

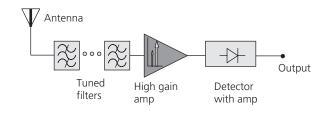

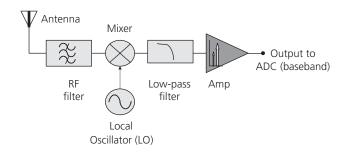

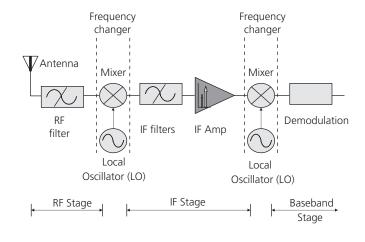

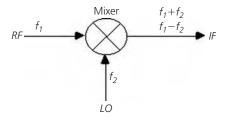

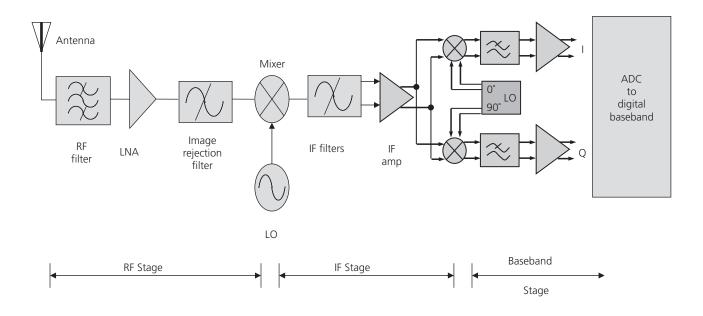

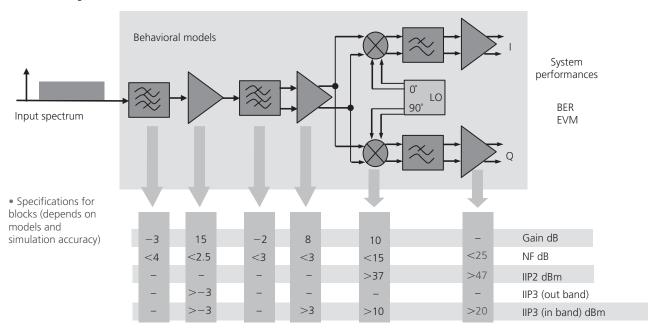

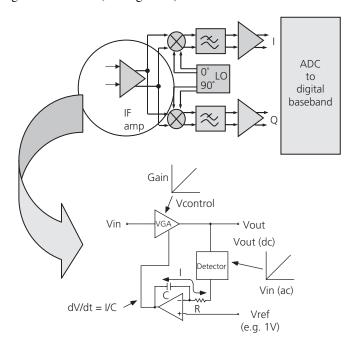

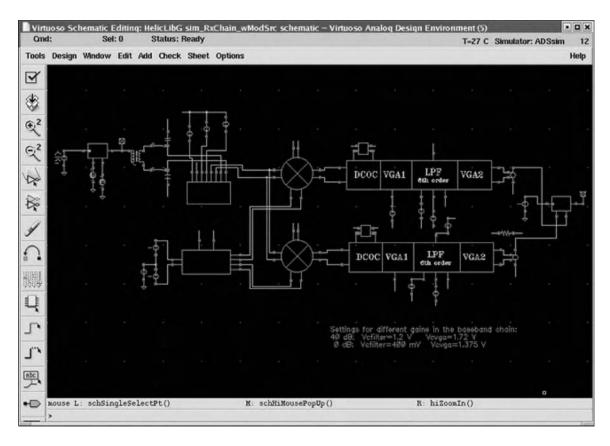

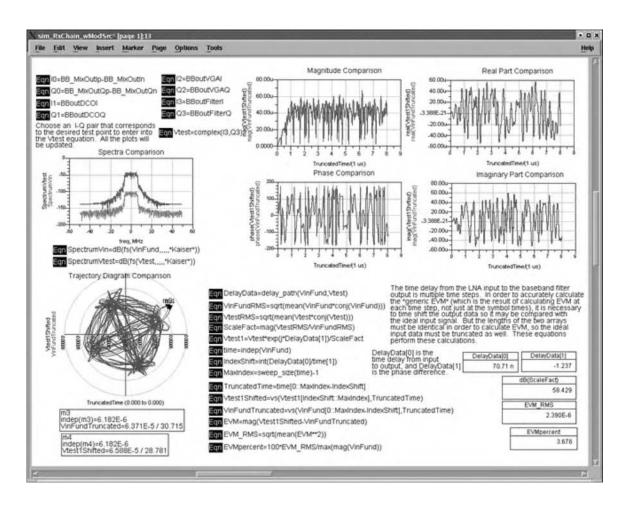

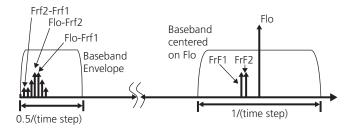

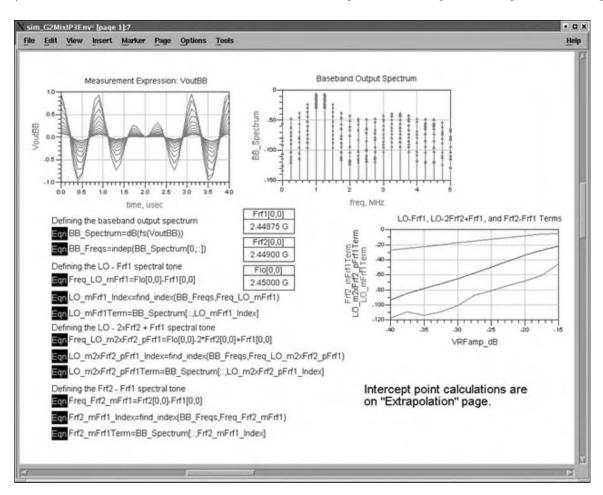

| CHAPTER 8 RF Front-End Design Higher Levels of Integration – Basic Receiver Architectures – ADC'S Effect on Front-End Design – Software Defined Radios – Case Study—Modern Communication Receiver                                                                                     | 185 |

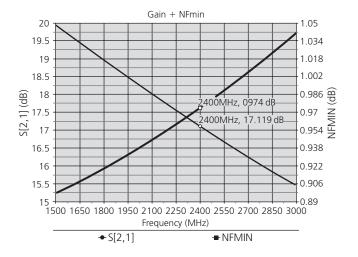

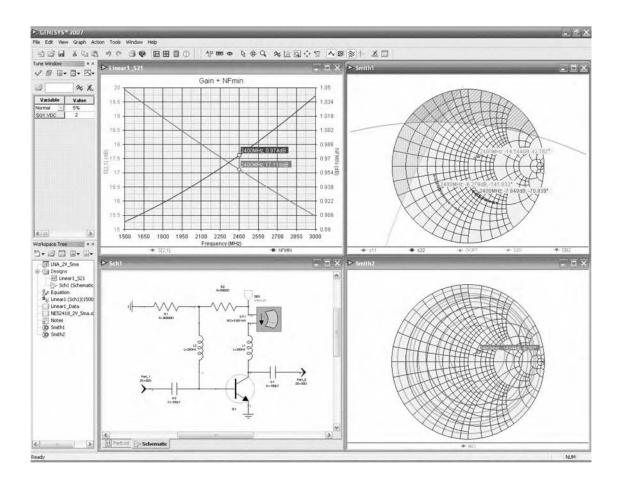

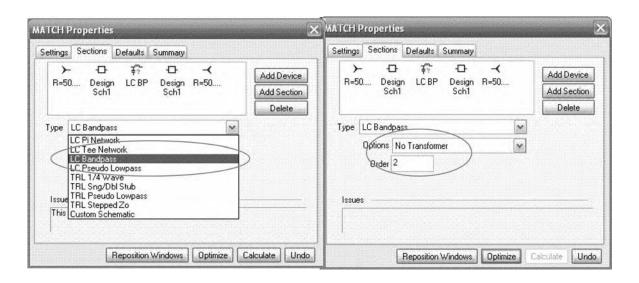

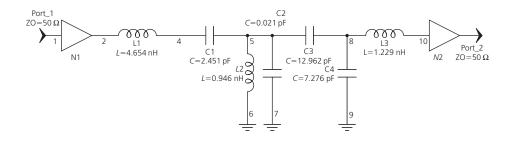

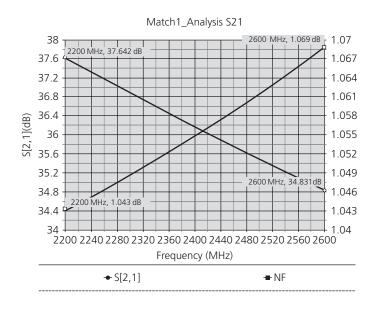

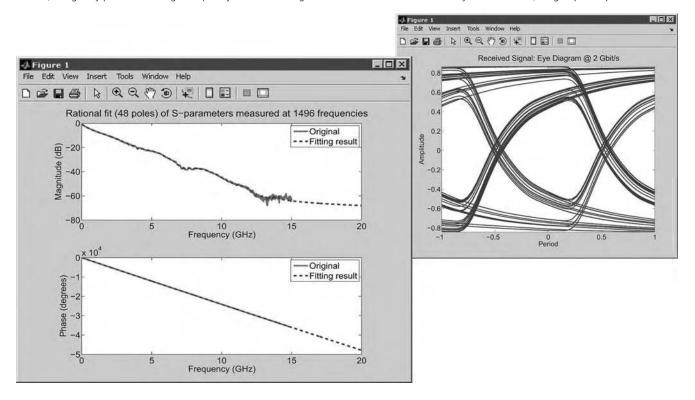

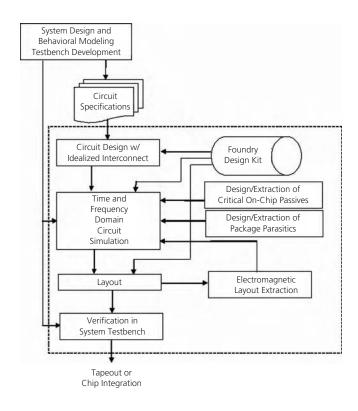

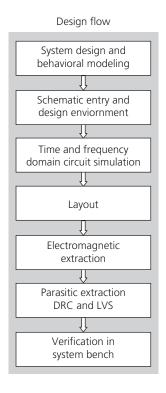

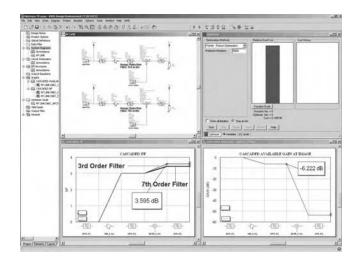

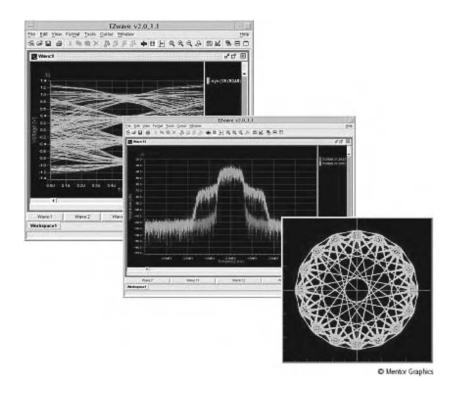

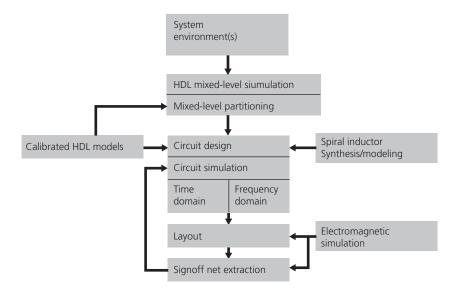

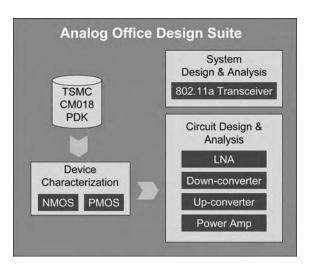

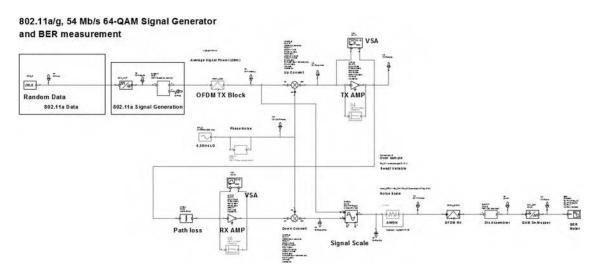

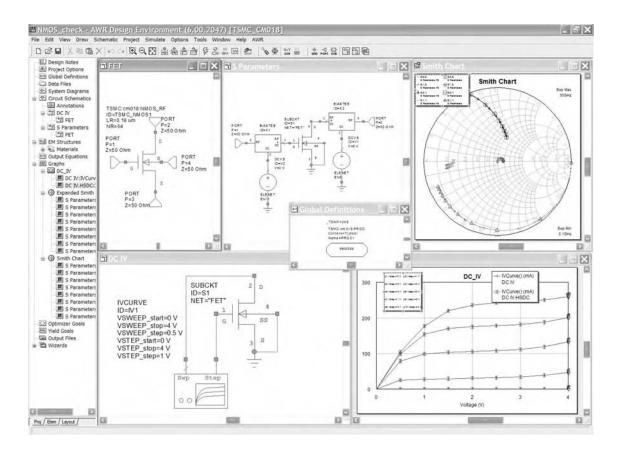

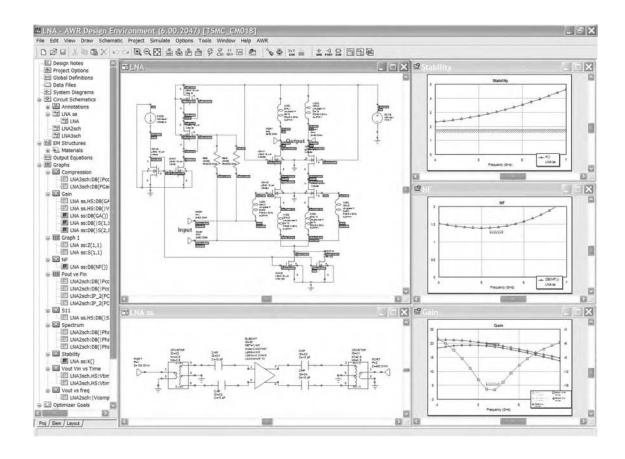

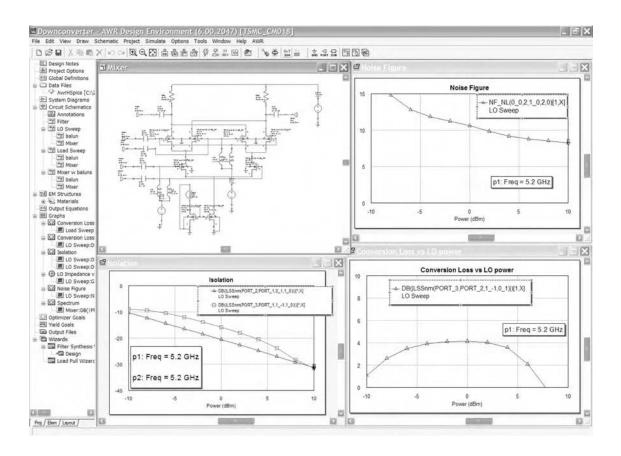

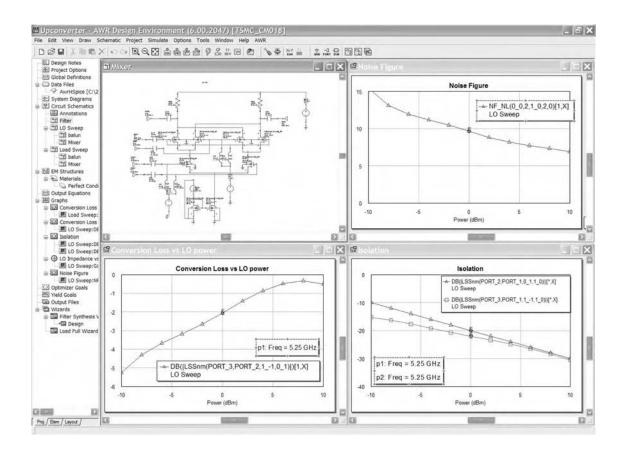

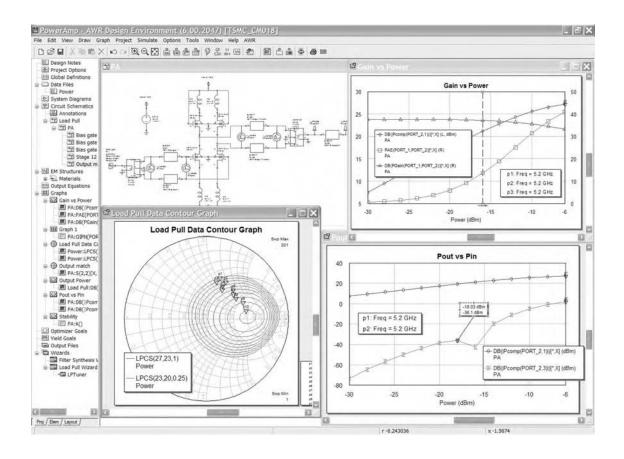

| CHAPTER 9 RF Design Tools Design Tool Basics – Design Languages – RFIC Design Flow – RFIC Design Flow Example – Simulation Example 1 – Simulation Example 2 – Modeling – PCB Design – Packaging – Case Study – Summary                                                                | 203 |

| APPENDIX A                                                                                                                                                                                                                                                                            | 227 |

| APPENDIX B                                                                                                                                                                                                                                                                            | 229 |

| BIBLIOGRAPHY                                                                                                                                                                                                                                                                          | 233 |

| INDEX                                                                                                                                                                                                                                                                                 | 237 |

#### **PREFACE**

A great deal has changed since Chris Bowick's *RF Circuit Design* was first published, some 25 years ago. In fact, we could just say that the RF industry has changed quite a bit since the days of Marconi and Tesla—both technological visionaries woven into the fabric of history as the men who enabled radio communications. Who could have envisioned that their innovations in the late 1800's would lay the groundwork for the eventual creation of the radio—a key component in all mobile and portable communications systems that exist today? Or, that their contributions would one day lead to such a compelling array of RF applications, ranging from radar to the cordless telephone and everything in between. Today, the radio stands as the backbone of the wireless industry. It is in virtually every wireless device, whether a cellular phone, measurement/instrumentation system used in manufacturing, satellite communications system, television or the WLAN.

Of course, back in the early 1980s when this book was first written, RF was generally seen as a defense/military technology. It was utilized in the United States weapons arsenal as well as for things like radar and anti-jamming devices. In 1985, that image of RF changed when the FCC essentially made several bands of wireless spectrum, the Industrial, Scientific, and Medical (ISM) bands, available to the public on a license-free basis. By doing so—and perhaps without even fully comprehending the momentum its actions would eventually create—the FCC planted the seeds of what would one day be a multibillion-dollar industry.

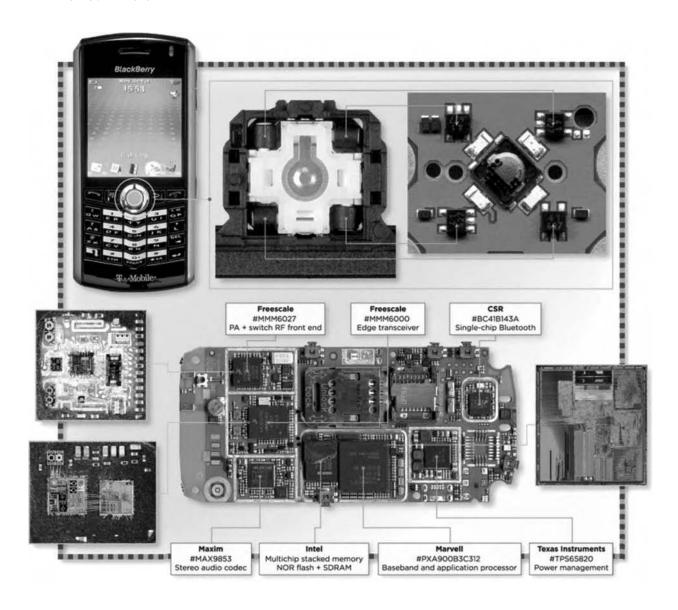

Today that industry is being driven not by aerospace and defense, but rather by the consumer demand for wireless applications that allow "anytime, anywhere" connectivity. And, it is being enabled by a range of new and emerging radio protocols such as Bluetooth<sup>®</sup>, Wi-Fi (802.11 WLAN), WiMAX, and ZigBee<sup>®</sup>, in addition to 3G and 4G cellular technologies like CDMA, EGPRS, GSM, and Long Term Evolution (LTE). For evidence of this fact, one needs look no further than the cellular handset. Within one decade, between roughly the years 1990 and 2000, this application emerged from a very small scale semiprofessional niche, to become an almost omnipresent device, with the number of users equal to 18% of the world population. Today, nearly 2 billion people use mobile phones on a daily basis—not just for their voice services, but for a growing number of social and mobile, data-centric Internet applications. Thanks to the mobile phone and service telecommunications industry revolution, average consumers today not only expect pervasive, ubiquitous mobility, they are demanding it.

But what will the future hold for the consumer RF application space? The answer to that question seems fairly well-defined as the RF industry now finds itself rallying behind a single goal: to realize true convergence. In other words, the future of the RF industry lies in its ability to enable next-generation mobile devices to cross all of the boundaries of the RF spectrum. Essentially then, this converged mobile device would bring together traditionally disparate functionality (e.g., mobile phone, television, PC and PDA) on the mobile platform.

Again, nowhere is the progress of the converged mobile device more apparent than with the cellular handset. It offers the ideal platform on which RF standards and technologies can converge to deliver a whole host of new functionality and capabilities that, as a society, we may not even yet be able to imagine. Movement in that direction has already begun. According to analysts with the IDC Worldwide Mobile Phone Tracker service, the converged mobile device market grew an estimated 42 percent in 2006 for a total of over 80 million units. In the fourth quarter alone, vendors shipped a total of 23.5 million devices, 33 percent more than the same quarter a year ago. That's a fairly remarkable accomplishment considering that, prior to the mid-nineties, the possibility of true RF convergence was thought unreachable. The mixing, sampling and direct-conversion technologies were simply deemed too clunky and limited to provide the foundation necessary for implementation of such a vision.

Regardless of how and when the goal of true convergence is finally realized, one thing has become imminently clear in the midst of all the growth and innovation of the past twenty five years—the RF industry is alive and well. More importantly, it is well primed for a future full of continuing innovation and market growth.

Of course, while all of these changes created a wealth of business opportunities in the RF industry, they also created new challenges for RF engineers pushing the limits of design further and further. Today, new opportunities signal new design challenges which engineers—whether experts in RF technology or not—will likely have to face.

One key challenge is how to accommodate the need for multi-band reception in cellular handsets. Another stems from the need for higher bandwidth at higher frequencies which, in turn, means that the critical dimensions of relevant parasitic elements shrink. As a result, layout elements that once could be ignored (e.g., interconnect, contact areas and holes, and bond pads) become non-negligible and influence circuit performance.

In response to these and other challenges, the electronics industry has innovated, and continues to innovate. Consider, for example, that roughly 25 years ago or so, electronic design automation (EDA) was just an infant industry, particularly for high-frequency RF and microwave engineering. While a few tools were commercially available, rather than use these solutions, most companies opted to develop their own high-frequency design tools. As the design process became more complex and the in-house tools too costly to develop and maintain, engineers turned to design automation to address their needs. Thanks to innovation from a variety of EDA companies, engineers now have access to a full gamut of RF/microwave EDA products and methodologies to aid them with everything from design and analysis to verification.

But the innovation doesn't stop there. RF front-end architectures have and will continue to evolve in step with cellular handsets sporting multi-band reception. Multi-band subsystems and shrinking element sizes have coupled with ongoing trends toward lower cost and decreasing time-to-market to create the need for tightly integrated RF front-ends and transceiver circuits. These high levels of system integration have in turn given rise to single-chip modules that incorporate front-end filters, amplifiers and mixes. But implementing single-chip RF front-end designs requires a balance of performance trade-offs between the interfacing subsystems, namely, the antenna and digital baseband systems. Achieving the required system performance when implementing integrated RF front-ends means that analog designers must now work more closely with their digital baseband counterpart, thus leading to greater integration of the traditional analog—digital design teams.

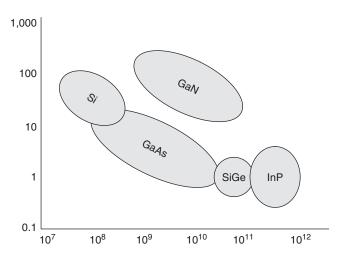

Other areas of innovation in the RF industry will come from improved RF power transistors that promise to give wireless infrastructure power amplifiers new levels of performance with better reliability and ruggedness. RFICs hope to extend the role of CMOS to enable emerging mobile handsets to deliver multimedia functions from a compact package at lower cost. Incumbents like gallium arsenide (GaAs) have moved to higher voltages to keep the pace going. Additionally, power amplifier-duplexer-filter modules will rapidly displace separate components in multi-band W-CDMA radios. Single-chip multimode transceivers will displace separate EDGE and W-CDMA/HSDPA transceivers in W-EDGE handsets. And, to better handle parasitic and high-speed effects on circuits, accurate modeling and back-annotation of ever-smaller layout elements will become critical, as will accurate electromagnetic (EM) modeling of RF on-chip structures like coils and interconnect.

Still further innovation will come from emerging technologies in RF such as gallium nitride and micro-electro-mechanical systems (MEMS). In the latter case, these advanced micromachined devices are being integrated with CMOS signal processing and conditioning circuits for high-volume markets such as mobile phones and portable electronics. According to market research firm ABI Research, by 2008 use of MEMs in mobile phones will take off. This is due to the technology's small size, flexibility and performance advantages, all of which are critical to enabling the adaptive, multifunction handsets of the future.

It is this type of innovation, coupled with the continuously changing landscape of existing application and market opportunities, which has prompted a renewed look at the content in *RF Circuit Design*. It quickly became clear that, in order for this book to continue to serve its purpose as your hands-on guide to RF circuit design, changes were required. As a result, this new 25<sup>th</sup> anniversary edition comes to you with updated information on existing topics like resonant circuits, impedance matching and RF amplifier design, as well as new content pertaining to RF front-end design and RF design tools. This information is applicable to any engineer working in today's dynamically changing RF industry, as well as for those true visionaries working on the cusp of the information/communication/entertainment market convergence which the RF industry now inspires.

Cheryl Ajluni and John Blyler

#### **ACKNOWLEDGMENTS**

No man—or woman—is an island. Many very busy people helped to make this update of Chris's original book possible. Here are just a few of the main contributors—old friends and new—who gave generously of their time and expertise in the review of the RF Front-End chapter of this book: Special thanks to George Zafiropoulos, VP of Marketing, at Synopsys for also rekindling my interest in amateur radio; Colin Warwick, RF Product Manager, The MathWorks, Inc., (Thanks for a very thorough review!); Rick Lazansky, R&D Manager, Agilent EEs of EDA; David Ewing, Director of Software Engineering at Synapse and George Opsahl, President of Clearbrook Technology.

One of the most challenging tasks in preparing any technical piece is the selection of the right case study. This task was made easier for me by the help of both Analog Devices, Inc., and by Jean Rousset, consultant to Agilent Technologies.

This update would not have been possible without the help of Cheryl Ajluni—my co-author, friend, and former editor of Penton's Wireless Systems Design magazine. Additional thanks to Jack Browne, editor of Microwave and RF magazine, for his insights and content sharing at a critical juncture during my writing. Last but not least, I thank the two most important people to any published book author—namely the acquisition editor, Rachel Roumeliotis and the project manager, Anne B. McGee at Elsevier. Great job, everyone!

John Blyler

This revised version of RF Circuit Design would not have been possible were it not for the tireless efforts of many friends and colleagues, to all of whom I offer my utmost gratitude and respect. Their technical contributions, reviews and honest opinions helped me more than they will ever know. With that said, I want to offer special thanks to Doron Aronson, Michael C'deBaca, Joseph Curcurio, John Dunn, Suzanne Graham, Sonia Harrison, Victoria Juarez de Savin, Jim Lev, Daren McClearnon, Tom Quan, Mark Ravenstahl, Craig Schmidt, Dave Smith, Janet Smith, Heidi Vantulden, and Per Viklund; as well as the following companies: Agilent Technologies, Ansoft, Applied Wave Research, Cadence Design Systems, Mentor Graphics, Microwave Software, and The MathWorks, Inc.

To all of the folks at Elsevier who contributed in some way to this book—Anne B. McGee, Ganesan Murugesan and Rachel Roumeliotis—your work ethic, constant assistance and patience have been very much appreciated.

To Cindy Shamieh, whose excellent research skills provided the basis for many of the revisions throughout this version of the book—your efforts and continued friendship mean the world to me.

And last, but certainly not least, to John Blyler my friend and co-author—thank you for letting me share this journey with you.

Cheryl Ajluni

# COMPONENTS and Systems

omponents, those bits and pieces which make up a radio frequency (RF) circuit, seem at times to be taken for granted. A capacitor is, after all, a capacitor—isn't it? A 1-megohm resistor presents an impedance of at least 1 megohm—doesn't it? The reactance of an inductor always increases with frequency, right? Well, as we shall see later in this discussion, things aren't always as they seem. Capacitors at certain frequencies may not be capacitors at all, but may look inductive, while inductors may look like capacitors, and resistors may tend to be a little of both.

In this chapter, we will discuss the properties of resistors, capacitors, and inductors at radio frequencies as they relate to circuit design. But, first, let's take a look at the most simple component of any system and examine its problems at radio frequencies.

#### WIRE

Wire in an RF circuit can take many forms. Wirewound resistors, inductors, and axial- and radial-leaded capacitors all use a wire of some size and length either in their leads, or in the actual body of the component, or both. Wire is also used in many interconnect applications in the lower RF spectrum. The behavior of a wire in the RF spectrum depends to a large extent on the wire's diameter and length. Table 1-1 lists, in the American Wire Gauge (AWG) system, each gauge of wire, its corresponding diameter, and other characteristics of interest to the RF circuit designer. In the AWG system, the diameter of a wire will roughly double every six wire gauges. Thus, if the last six gauges and their corresponding diameters are memorized from the chart, all other wire diameters can be determined without the aid of a chart (Example 1-1).

#### Skin Effect

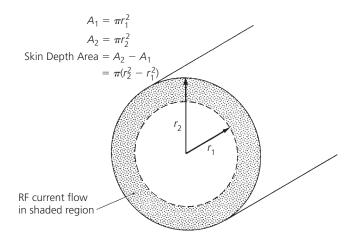

A conductor, at low frequencies, utilizes its entire cross-sectional area as a transport medium for charge carriers. As the frequency is increased, an increased magnetic field at the center of the conductor presents an impedance to the charge carriers, thus decreasing the current density at the center of the conductor and increasing the current density around its perimeter. This increased current density near the edge of the conductor is known as *skin effect*. It occurs in all conductors including resistor leads, capacitor leads, and inductor leads.

#### **EXAMPLE 1-1**

Given that the diameter of AWG 50 wire is 1.0 mil (0.001 inch), what is the diameter of AWG 14 wire?

Solution

AWG 50 = 1 mil

AWG  $44 = 2 \times 1 \text{ mil} = 2 \text{ mils}$

AWG  $38 = 2 \times 2 \text{ mils} = 4 \text{ mils}$

AWG  $32 = 2 \times 4 \text{ mils} = 8 \text{ mils}$

AWG  $26 = 2 \times 8 \text{ mils} = 16 \text{ mils}$

AWG  $20 = 2 \times 16 \text{ mils} = 32 \text{ mils}$

AWG  $14 = 2 \times 32 \text{ mils} = 64 \text{ mils} (0.064 \text{ inch})$

The depth into the conductor at which the charge-carrier current density falls to 1/e, or 37% of its value along the surface, is known as the *skin depth* and is a function of the frequency and the permeability and conductivity of the medium. Thus, different conductors, such as silver, aluminum, and copper, all have different skin depths.

The net result of skin effect is an effective decrease in the cross-sectional area of the conductor and, therefore, a net increase in the ac resistance of the wire as shown in Fig. 1-1. For copper, the skin depth is approximately 0.85 cm at 60 Hz and 0.007 cm at 1 MHz. Or, to state it another way: 63% of the RF current flowing in a copper wire will flow within a distance of 0.007 cm of the outer edge of the wire.

#### **Straight-Wire Inductors**

In the medium surrounding any current-carrying conductor, there exists a magnetic field. If the current in the conductor is an alternating current, this magnetic field is alternately expanding and contracting and, thus, producing a voltage on the wire which opposes any change in current flow. This opposition to change is called *self-inductance* and we call anything that possesses this quality an *inductor*. Straight-wire inductance might seem trivial, but as will be seen later in the chapter, the higher we go in frequency, the more important it becomes.

FIG. 1-1. Skin depth area of a conductor.

The inductance of a straight wire depends on both its length and its diameter, and is found by:

$$L = 0.002 l \left[ 2.3 \log \left( \frac{4l}{d} \right) - 0.75 \right] \mu \text{H}$$

(Eq. 1-1)

where,

L = the inductance in  $\mu$ H,

l = the length of the wire in cm,

d = the diameter of the wire in cm.

This is shown in calculations of Example 1-2.

#### **EXAMPLE 1-2**

Find the inductance of 5 centimeters of No. 22 copper wire.

Solution

From Table 1-1, the diameter of No. 22 copper wire is 25.3 mils. Since 1 mil equals  $2.54 \times 10^{-3}$  cm, this equals 0.0643 cm. Substituting into Equation 1-1 gives

$$L = (0.002)(5) \left[ 2.3 \log \left( \frac{4(5)}{0.0643} \right) - 0.75 \right]$$

= 50 nanohenries

The concept of inductance is important because any and all conductors at radio frequencies (including hookup wire, capacitor leads, etc.) tend to exhibit the property of inductance. Inductors will be discussed in greater detail later in this chapter.

#### **RESISTORS**

Resistance is the property of a material that determines the rate at which electrical energy is converted into heat energy for a given

electric current. By definition:

1 volt across 1 ohm = 1 coulomb per second = 1 ampere

The thermal dissipation in this circumstance is 1 watt.

$$P = EI$$

= 1 volt × 1 ampere

= 1 watt

Resistors are used everywhere in circuits, as transistor bias networks, pads, and signal combiners. However, very rarely is there any thought given to how a resistor actually behaves once we depart from the world of direct current (DC). In some instances, such as in transistor biasing networks, the resistor will still perform its DC circuit function, but it may also disrupt the circuit's RF operating point.

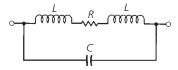

#### Resistor Equivalent Circuit

The equivalent circuit of a resistor at radio frequencies is shown in Fig. 1-2. R is the resistor value itself, L is the lead inductance, and C is a combination of parasitic capacitances which varies from resistor to resistor depending on the resistor's structure. Carbon-composition resistors are notoriously poor high-frequency performers. A carbon-composition resistor consists of densely packed dielectric particulates or carbon granules. Between each pair of carbon granules is a very small parasitic capacitor. These parasitics, in aggregate, are not insignificant, however, and are the major component of the device's equivalent circuit.

FIG. 1-2. Resistor equivalent circuit.

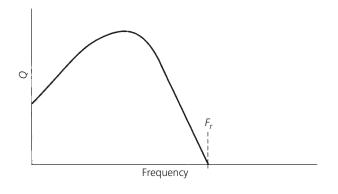

Wirewound resistors have problems at radio frequencies too. As may be expected, these resistors tend to exhibit widely varying impedances over various frequencies. This is particularly true of the low resistance values in the frequency range of  $10\,\mathrm{MHz}$  to  $200\,\mathrm{MHz}$ . The inductor L, shown in the equivalent circuit of Fig. 1-2, is much larger for a wirewound resistor than for a carbon-composition resistor. Its value can be calculated using the single-layer air-core inductance approximation formula. This formula is discussed later in this chapter. Because wirewound resistors look like inductors, their impedances will first increase as the frequency increases. At some frequency ( $F_{\mathrm{r}}$ ), however, the inductance (L) will resonate with the shunt capacitance (C), producing an impedance peak. Any further increase in frequency will cause the resistor's impedance to decrease as shown in Fig. 1-3.

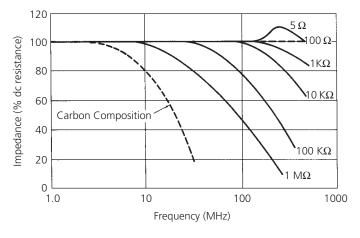

A metal-film resistor seems to exhibit the best characteristics over frequency. Its equivalent circuit is the same as the

FIG. 1-3. Impedance characteristic of a wirewound resistor.

carbon-composition and wirewound resistor, but the values of the individual parasitic elements in the equivalent circuit decrease.

The impedance of a metal-film resistor tends to decrease with frequency above about 10 MHz, as shown in Fig. 1-4. This is due to the shunt capacitance in the equivalent circuit. At very high frequencies, and with low-value resistors (under 50  $\Omega$ ), lead inductance and skin effect may become noticeable. The lead inductance produces a resonance peak, as shown for the 5  $\Omega$  resistance in Fig. 1-4, and skin effect decreases the slope of the curve as it falls off with frequency.

FIG. 1-4. Frequency characteristics of metal-film vs. carbon-composition resistors. (Adapted from *Handbook of Components for Electronics*, McGraw-Hill)

Many manufacturers will supply data on resistor behavior at radio frequencies but it can often be misleading. Once you understand the mechanisms involved in resistor behavior, however, it will not matter in what form the data is supplied. Example 1-3 illustrates that fact.

The recent trend in resistor technology has been to eliminate or greatly reduce the stray reactances associated with resistors. This has led to the development of thin-film chip resistors, such as

#### **EXAMPLE 1-3**

In Fig. 1-2, the lead lengths on the metal-film resistor are 1.27 cm (0.5 inch), and are made up of No. 14 wire. The total stray shunt capacitance (*C*) is 0.3 pF. If the resistor value is 10,000 ohms, what is its equivalent RF impedance at 200 MHz?

#### Solution

From Table 1-1, the diameter of No. 14 AWG wire is 64.1 mils (0.1628 cm). Therefore, using Equation 1-1:

$$L = (0.002)(1.27) \left[ 2.3 \log \left( \frac{4(1.27)}{0.1628} - 0.75 \right) \right]$$

= 8.7 nanohenries

This presents an equivalent reactance at 200 MHz of:

$$X_L = \omega L$$

=  $2\pi (200 \times 10^6)(8.7 \times 10^{-9})$

= 10.93 ohms

The capacitor (C) presents an equivalent reactance of:

$$X_{c} = \frac{1}{\omega C}$$

$$= \frac{1}{2\pi (200 \times 10^{6})(0.3 \times 10^{-12})}$$

$$= 2653$$

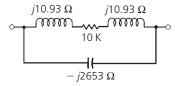

The combined equivalent circuit for this resistor, at 200 MHz, is shown in Fig. 1-5.

FIG. 1-5. Equivalent circuit values for Example 1-3.

From this sketch, we can see that, in this case, the lead inductance is insignificant when compared with the 10K series resistance and it may be neglected. The parasitic capacitance, on the other hand, cannot be neglected. What we now have, in effect, is a  $2653~\Omega$  reactance in parallel with a  $10,000~\Omega$  resistance. The magnitude of the combined impedance is:

$$Z = \frac{RX_e}{\sqrt{R^2 + X_e^2}}$$

$$= \frac{(10K)(2653)}{\sqrt{(10K)^2 + (2653)^2}}$$

$$= 25643 \text{ ohms}$$

Thus, our 10K resistor looks like 2564 ohms at 200 MHz.

those shown in Fig. 1-6. They are typically produced on alumina or beryllia substrates and offer very little parasitic reactance at frequencies from DC to 2 GHz.

FIG. 1-6. Thin-film resistors. (Courtesy of Vishay Intertechnology)

#### **CAPACITORS**

Capacitors are used extensively in RF applications, such as bypassing, interstage coupling, and in resonant circuits and filters. It is important to remember, however, that not all capacitors lend themselves equally well to each of the above-mentioned applications. The primary task of the RF circuit designer, with regard to capacitors, is to choose the best capacitor for his particular application. Cost effectiveness is usually a major factor in the selection process and, thus, many trade-offs occur. In this section, we'll take a look at the capacitor's equivalent circuit and we will examine a few of the various types of capacitors used at radio frequencies to see which are best suited for certain applications. But first, a little review.

#### Parallel-Plate Capacitor

A capacitor is any device which consists of two conducting surfaces separated by an insulating material or dielectric. The dielectric is usually ceramic, air, paper, mica, plastic, film, glass, or oil. The capacitance of a capacitor is that property which permits the storage of a charge when a potential difference exists between the conductors. Capacitance is measured in units of farads. A 1-farad capacitor's potential is raised by 1 volt when it receives a charge of 1 coulomb.

$$C = \frac{Q}{V}$$

where,

C = capacitance in farads,

Q =charge in coulombs,

V = voltage in volts.

However, the farad is much too impractical to work with, so smaller units were devised.

1 microfarad =

$$1 \mu F = 1 \times 10^{-6}$$

farad

1 picofarad =  $1 pF = 1 \times 10^{-12}$  farad

As stated previously, a capacitor in its fundamental form consists of two metal plates separated by a dielectric material of some sort. If we know the area (A) of each metal plate, the distance (d) between the plate (in inches), and the permittivity  $(\varepsilon)$  of the dielectric material in farads/meter (f/m), the capacitance of a parallel-plate capacitor can be found by:

$$C = \frac{0.2249\varepsilon A}{d\varepsilon_0} \text{ picofarads}$$

(Eq. 1-2)

where

$$\varepsilon_0$$

= free-space permittivity =  $8.854 \times 10^{-12}$  f/m.

In Equation 1-2, the area (A) must be large with respect to the distance (d). The ratio of  $\varepsilon$  to  $\varepsilon_0$  is known as the dielectric constant (k) of the material. The dielectric constant is a number that provides a comparison of the given dielectric with air (see Fig. 1-7). The ratio of  $\varepsilon/\varepsilon_0$  for air is, of course, 1. If the dielectric constant of a material is greater than 1, its use in a capacitor as a dielectric will permit a greater amount of capacitance for the same dielectric thickness as air. Thus, if a material's dielectric constant is 3, it will produce a capacitor having three times the capacitance of one that has air as its dielectric. For a given value of capacitance, then, higher dielectric-constant materials will produce physically smaller capacitors. But, because the dielectric plays such a major role in determining the capacitance of a capacitor, it follows that the influence of a dielectric on capacitor operation, over frequency and temperature, is often important.

| Dielectric       | K          |

|------------------|------------|

| Air              | 1          |

| Polystrene       | 2.5        |

| Paper            | 4          |

| Mica             | 5          |

| Ceramic (low K)  | 10         |

| Ceramic (high K) | 100-10,000 |

FIG. 1-7. Dielectric constants of some common materials.

#### **Real-World Capacitors**

The usage of a capacitor is primarily dependent upon the characteristics of its dielectric. The dielectric's characteristics also determine the voltage levels and the temperature extremes at which the device may be used. Thus, any losses or imperfections in the dielectric have an enormous effect on circuit operation.

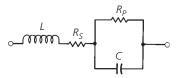

The equivalent circuit of a capacitor is shown in Fig. 1-8, where C equals the capacitance,  $R_s$  is the heat-dissipation loss expressed either as a power factor (PF) or as a dissipation factor (DF),  $R_p$

FIG. 1-8. Capacitor equivalent circuit.

is the insulation resistance, and L is the inductance of the leads and plates. Some definitions are needed now.

*Power Factor*—In a *perfect* capacitor, the alternating current will lead the applied voltage by 90°. This phase angle  $(\phi)$  will be smaller in a real capacitor due to the total series resistance  $(R_s + R_p)$  that is shown in the equivalent circuit. Thus,

$$PF = \cos \phi$$

The power factor is a function of temperature, frequency, and the dielectric material.

Insulation Resistance—This is a measure of the amount of DC current that flows through the dielectric of a capacitor with a voltage applied. No material is a perfect insulator; thus, some leakage current must flow. This current path is represented by  $R_p$  in the equivalent circuit and, typically, it has a value of 100,000 megohms or more.

Effective Series Resistance—Abbreviated ESR, this resistance is the combined equivalent of  $R_s$  and  $R_p$ , and is the AC resistance of a capacitor.

$$ESR = \frac{PF}{\omega C} (1 \times 10^6)$$

where

$$\omega = 2\pi f$$

Dissipation Factor – The DF is the ratio of AC resistance to the reactance of a capacitor and is given by the formula:

$$DF = \frac{ESR}{X_c} \times 100\%$$

Q – The Q of a circuit is the reciprocal of DF and is defined as the quality factor of a capacitor.

$$Q = \frac{1}{DF} = \frac{X_c}{ESR}$$

Thus, the larger the Q, the better the capacitor.

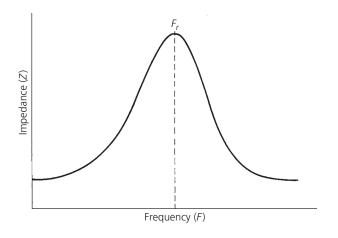

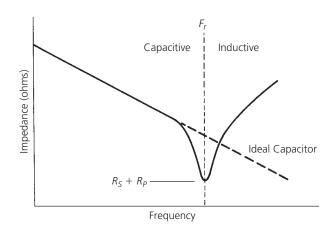

The effect of these imperfections in the capacitor can be seen in the graph of Fig. 1-9. Here, the impedance characteristic of an ideal capacitor is plotted against that of a real-world capacitor. As shown, as the frequency of operation increases, the lead inductance becomes important. Finally, at  $F_r$ , the inductance becomes series resonant with the capacitor. Then, above  $F_r$ , the capacitor acts like an inductor. In general, larger-value capacitors tend to exhibit more internal inductance than smaller-value capacitors. Therefore, depending upon its internal structure, a

FIG. 1-9. Impedance characteristic vs. frequency.

0.1- $\mu F$  capacitor may not be as good as a 300-pF capacitor in a bypass application at 250 MHz. In other words, the classic formula for capacitive reactance,  $X_e = \frac{1}{\omega C}$ , might seem to indicate that larger-value capacitors have less reactance than smaller-value capacitors at a given frequency. At RF frequencies, however, the opposite may be true. At certain higher frequencies, a 0.1- $\mu F$  capacitor might present a higher impedance to the signal than would a 330-pF capacitor. This is something that must be considered when designing circuits at frequencies above 100 MHz. Ideally, each component that is to be used in any VHF, or higher frequency, design should be examined on a network analyzer similar to the one shown in Fig. 1-10. This will allow the designer to know exactly what he is working with before it goes into the circuit.

FIG. 1-10. Agilent E5071C Network Analyzer.

#### **Capacitor Types**

There are many different dielectric materials used in the fabrication of capacitors, such as paper, plastic, ceramic, mica, polystyrene, polycarbonate, teflon, oil, glass, and air. Each material has its advantages and disadvantages. The RF designer

is left with a myriad of capacitor types that he could use in any particular application and the ultimate decision to use a particular capacitor is often based on convenience rather than good sound judgment. In many applications, this approach simply cannot be tolerated. This is especially true in manufacturing environments where more than just one unit is to be built and where they must operate reliably over varying temperature extremes. It is often said in the engineering world that anyone can design something and make it work *once*, but it takes a good designer to develop a unit that can be produced in quantity and still operate as it should in different temperature environments.

#### Ceramic Capacitors

Ceramic dielectric capacitors vary widely in both dielectric constant (k = 5 to 10,000) and temperature characteristics. A good rule of thumb to use is: "The higher the k, the worse is its temperature characteristic." This is shown quite clearly in Fig. 1-11.

FIG. 1-11. Temperature characteristics for ceramic dielectric capacitors.

As illustrated, low-k ceramic capacitors tend to have linear temperature characteristics. These capacitors are generally manufactured using both magnesium titanate, which has a positive temperature coefficient (TC), and calcium titanate which has a negative TC. By combining the two materials in varying proportions, a range of controlled temperature coefficients can be generated. These capacitors are sometimes called temperature compensating capacitors, or NPO (negative positive zero) ceramics. They can have TCs that range anywhere from +150 to -4700 ppm/°C (parts-per-million-per-degree-Celsius) with

tolerances as small as  $\pm 15 \,\mathrm{ppm/^{\circ}C}$ . Because of their excellent temperature stability, NPO ceramics are well suited for oscillator, resonant circuit, or filter applications.

Moderately stable ceramic capacitors (Fig. 1-11) typically vary  $\pm 15\%$  of their rated capacitance over their temperature range. This variation is typically nonlinear, however, and care should be taken in their use in resonant circuits or filters where stability is important. These ceramics are generally used in switching circuits. Their main advantage is that they are generally smaller than the NPO ceramic capacitors and, of course, cost less.

High-K ceramic capacitors are typically termed general-purpose capacitors. Their temperature characteristics are very poor and their capacitance may vary as much as 80% over various temperature ranges (Fig. 1-11). They are commonly used only in bypass applications at radio frequencies.

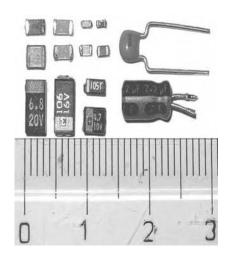

There are ceramic capacitors available on the market which are specifically intended for RF applications. These capacitors are typically high-Q (low ESR) devices with flat ribbon leads or with no leads at all. The lead material is usually solid silver or silver plated and, thus, contains very low resistive losses. At VHF frequencies and above, these capacitors exhibit very low lead inductance due to the flat ribbon leads. These devices are, of course, more expensive and require special printed-circuit board areas for mounting. The capacitors that have no leads are called chip capacitors. These capacitors are typically used above 500 MHz where lead inductance cannot be tolerated. Chip capacitors and flat ribbon capacitors are shown in Fig. 1-12.

FIG. 1-12. Chip and ceramic capacitors. (Courtesy of Wikipedia)

#### Mica Capacitors

Mica capacitors typically have a dielectric constant of about 6, which indicates that for a particular capacitance value, mica capacitors are typically large. Their low k, however, also produces an extremely good temperature characteristic. Thus, mica capacitors are used extensively in resonant circuits and in filters where PC board area is of no concern.

Silvered mica capacitors are even more stable. Ordinary mica capacitors have plates of foil pressed against the mica dielectric. In silvered micas, the silver plates are applied by a process called *vacuum evaporation* which is a much more exacting process. This produces an even better stability with very tight and reproducible tolerances of typically  $+20 \,\mathrm{ppm/^\circ C}$  over a range  $-60 \,\mathrm{^\circ C}$  to  $+89 \,\mathrm{^\circ C}$ .

The problem with micas, however, is that they are becoming increasingly less cost effective than ceramic types. Therefore, if you have an application in which a mica capacitor would seem to work well, chances are you can find a less expensive NPO ceramic capacitor that will work just as well.

#### Metalized-Film Capacitors

"Metalized-film" is a broad category of capacitor encompassing most of the other capacitors listed previously and which we have not yet discussed. This includes teflon, polystyrene, polycarbonate, and paper dielectrics.

Metalized-film capacitors are used in a number of applications, including filtering, bypassing, and coupling. Most of the polycarbonate, polystyrene, and teflon styles are available in very tight ( $\pm 2\%$ ) capacitance tolerances over their entire temperature range. Polystyrene, however, typically cannot be used over  $+85^{\circ}$ C as it is very temperature sensitive above this point. Most of the capacitors in this category are typically larger than the equivalent-value ceramic types and are used in applications where space is not a constraint.

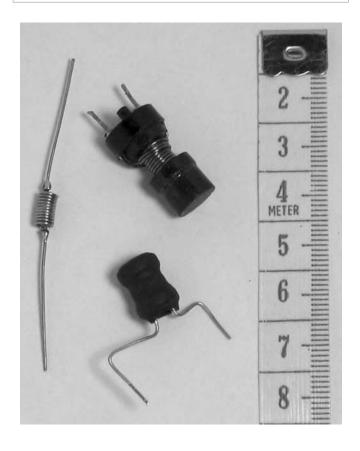

#### **INDUCTORS**

An inductor is nothing more than a wire wound or coiled in such a manner as to increase the magnetic flux linkage between the turns of the coil (see Fig. 1-13). This increased flux linkage increases the wire's self-inductance (or just plain inductance) beyond that which it would otherwise have been. Inductors are

used extensively in RF design in resonant circuits, filters, phase shift and delay networks, and as RF chokes used to prevent, or at least reduce, the flow of RF energy along a certain path.

#### Real-World Inductors

As we have discovered in previous sections of this chapter, there is no "perfect" component, and inductors are certainly no exception. As a matter of fact, of the components we have discussed, the inductor is probably the component most prone to very drastic changes over frequency.

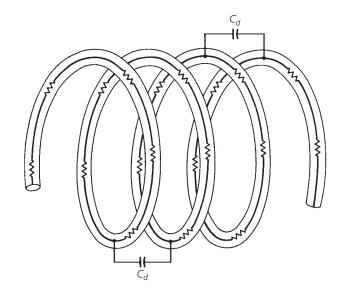

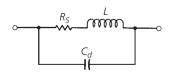

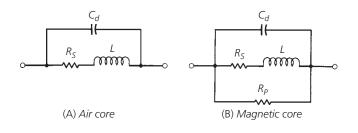

Fig. 1-14 shows what an inductor really looks like at RF frequencies. As previously discussed, whenever we bring two conductors into close proximity but separated by a dielectric, and place a voltage differential between the two, we form a capacitor. Thus, if any wire resistance at all exists, a voltage drop (even though very minute) will occur between the windings, and small capacitors will be formed. This effect is shown in Fig. 1-14 and is called distributed capacitance ( $C_d$ ). Then, in Fig. 1-15, the capacitance ( $C_d$ ) is an aggregate of the individual parasitic distributed capacitances of the coil shown in Fig. 1-14.

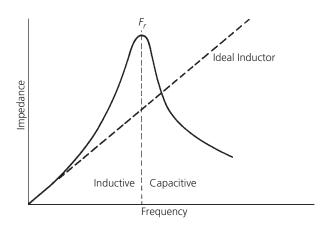

The effect of  $C_d$  upon the reactance of an inductor is shown in Fig. 1-16. Initially, at lower frequencies, the inductor's reactance parallels that of an ideal inductor. Soon, however, its reactance departs from the ideal curve and increases at a much faster rate until it reaches a peak at the inductor's parallel resonant frequency  $(F_r)$ . Above  $F_r$ , the inductor's reactance begins to

FIG. 1-14. Distributed capacitance and series resistance in an inductor.

FIG. 1-13. Simple inductors. (Courtesy of Wikipedia)

FIG. 1-15. Inductor equivalent circuit.

FIG. 1-16. Impedance characteristic vs. frequency for a practical and an ideal inductor.

#### **EXAMPLE 1-4**

To show that the impedance of a lossless inductor at resonance is infinite, we can write the following:

$$Z = \frac{X_L X_C}{X_L + X_C}$$

(Eq. 1-3)

where

Z = the impedance of the parallel circuit,

$X_L$  = the inductive reactance ( $j\omega L$ ),

$X_C$  = the capacitive reactance  $\left(\frac{1}{i\omega C}\right)$ .

Therefore,

$$Z = \frac{j\omega L\left(\frac{1}{j\omega C}\right)}{j\omega L + \frac{1}{i\omega C}}$$

(Eq. 1-4)

Multiplying numerator and denominator by  $j\omega C$ , we get:

$$Z = \frac{j\omega L}{(j\omega L)(j\omega C) + 1}$$

$$= \frac{j\omega L}{j^2 \omega^2 LC + 1}$$

(Eq.1-5)

From algebra,  $j^2 = -1$ ; then, rearranging:

$$Z = \frac{j\omega L}{1 - \omega^2 LC}$$

(Eq.1-6)

If the term  $\omega^2 LC$ , in Equation 1-6, should ever become equal to 1, then the denominator will be equal to zero and impedance Z will become infinite. The frequency at which  $\omega^2 LC$  becomes equal to 1 is:

$$\omega^{2}LC = 1$$

$$LC = \frac{1}{\omega^{2}}$$

$$\sqrt{LC} = \frac{1}{\omega}$$

$$2\pi\sqrt{LC} = \frac{1}{f}$$

#### **EXAMPLE 4-4—Cont**

$$\frac{1}{2\pi\sqrt{LC}} = f \tag{Eq.1-7}$$

which is the familiar equation for the resonant frequency of a tuned circuit.

FIG. 1-17. Chip inductors. (Courtesy of Wikipedia)

decrease with frequency and, thus, the inductor begins to look like a capacitor. Theoretically, the resonance peak would occur at infinite reactance (see Example 1-4). However, due to the series resistance of the coil, some finite impedance is seen at resonance.

Recent advances in inductor technology have led to the development of microminiature fixed-chip inductors. One type is shown in Fig. 1-17. These inductors feature a ceramic substrate with gold-plated solderable wrap-around bottom connections. They come in values from  $0.01\,\mu\mathrm{H}$  to  $1.0\,\mathrm{mH}$ , with typical  $Q\mathrm{s}$  that range from 40 to 60 at  $200\,\mathrm{MHz}$ .

It was mentioned earlier that the series resistance of a coil is the mechanism that keeps the impedance of the coil finite at resonance. Another effect it has is to broaden the resonance peak of the impedance curve of the coil. This characteristic of resonant circuits is an important one and will be discussed in detail in Chapter 3.

FIG. 1-18. The Q variation of an inductor vs. frequency.

The ratio of an inductor's reactance to its series resistance is often used as a measure of the quality of the inductor. The larger the ratio, the better is the inductor. This quality factor is referred to as the Q of the inductor.

$$Q = \frac{X}{R_c}$$

If the inductor were wound with a perfect conductor, its Q would be infinite and we would have a lossless inductor. Of course, there is no perfect conductor and, thus, an inductor always has some finite Q.

At low frequencies, the Q of an inductor is very good because the only resistance in the windings is the dc resistance of the wire—which is very small. But as the frequency increases, skin effect and winding capacitance begin to degrade the quality of the inductor. This is shown in the graph of Fig. 1-18. At low frequencies, Q will increase directly with frequency because its reactance is increasing and skin effect has not yet become noticeable. Soon, however, skin effect does become a factor. The Q still rises, but at a lesser rate, and we get a gradually decreasing slope in the curve. The flat portion of the curve in Fig. 1-18 occurs as the series resistance and the reactance are changing at the same rate. Above this point, the shunt capacitance and skin effect of the windings combine to decrease the Q of the inductor to zero at its resonant frequency.

Some methods of increasing the Q of an inductor and extending its useful frequency range are:

- 1. Use a larger diameter wire. This decreases the AC and DC resistance of the windings.

- 2. Spread the windings apart. Air has a lower dielectric constant than most insulators. Thus, an air gap between the windings decreases the interwinding capacitance.

- 3. Increase the permeability of the flux linkage path. This is most often done by winding the inductor around a magnetic-core material, such as iron or ferrite. A coil made in this manner will also consist of fewer turns for a given inductance. This will be discussed in a later section of this chapter.

FIG. 1-19. Single-layer air-core inductor requirements.

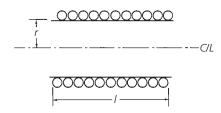

#### Single-Layer Air-Core Inductor Design

Every RF circuit designer needs to know how to design inductors. It may be tedious at times, but it's well worth the effort. The formula that is generally used to design single-layer air-core inductors is given in Equation 1-8 and diagrammed in Fig. 1-19.

$$L = \frac{0.394r^2N^2}{9r + 10l}$$

(Eq. 1-8)

where

r = the coil radius in cm,

l = the coil length in cm,

L = the inductance in microhenries.

However, coil length l must be greater than 0.67r. This formula is accurate to within one percent. See Example 1-5.

#### **EXAMPLE 1-5**

Design a 100 nH (0.1  $\mu$ H) air-core inductor on a 1/4-inch (0.635 cm) coil form.

Solution

For optimum Q, the length of the coil should be equal to its diameter. Thus,  $l=0.635\,\mathrm{cm}$ ,  $r=0.317\,\mathrm{cm}$ , and  $L=0.1\,\mu\mathrm{H}$ .

Using Equation 1-8 and solving for N gives:

$$N = \sqrt{\frac{29L}{0.394r}}$$

where we have taken l = 2r, for optimum Q.

Substituting and solving:

$$N = \sqrt{\frac{29(0.1)}{(0.394)(0.317)}}$$

$$= 4.8 \text{ turns}$$

Thus, we need 4.8 turns of wire within a length of 0.635 cm. A look at Table 1-1 reveals that the largest diameter enamel-coated wire that will allow 4.8 turns in a length of 0.635 cm is No. 18 AWG wire which has a diameter of 42.4 mils (0.107 cm).

| Wire<br>Size<br>(AWG) | Dia<br>in Mils*<br>(Bare) | Dia<br>in Mils<br>(Coated) | Ohms/<br>1000 ft. | Area<br>Circular<br>Mils | Wire<br>Size<br>(AWG) | Dia<br>in Mils*<br>(Bare) | Dia<br>in Mils<br>(Coated) | Ohms/<br>1000 ft. | Area<br>Circular<br>Mils |

|-----------------------|---------------------------|----------------------------|-------------------|--------------------------|-----------------------|---------------------------|----------------------------|-------------------|--------------------------|

| 1                     | 289.3                     |                            | 0.124             | 83690                    | 26                    | 15.9                      | 17.2                       | 41.0              | 253                      |

| 2                     | 257.6                     |                            | 0.156             | 66360                    | 27                    | 14.2                      | 15.4                       | 51.4              | 202                      |

| 3                     | 229.4                     |                            | 0.197             | 52620                    | 28                    | 12.6                      | 13.8                       | 65.3              | 159                      |

| 4                     | 204.3                     |                            | 0.249             | 41740                    | 29                    | 11.3                      | 12.3                       | 81.2              | 123                      |

| 5                     | 181.9                     |                            | 0.313             | 33090                    | 30                    | 10.0                      | 11.0                       | 104.0             | 100                      |

| 6                     | 162.0                     |                            | 0.395             | 26240                    | 31                    | 8.9                       | 9.9                        | 131               | 79.2                     |

| 7                     | 144.3                     |                            | 0.498             | 20820                    | 32                    | 8.0                       | 8.8                        | 162               | 64.0                     |

| 8                     | 128.5                     | 131.6                      | 0.628             | 16510                    | 33                    | 7.1                       | 7.9                        | 206               | 50.4                     |

| 9                     | 114.4                     | 116.3                      | 0.793             | 13090                    | 34                    | 6.3                       | 7.0                        | 261               | 39.7                     |

| 10                    | 101.9                     | 104.2                      | 0.999             | 10380                    | 35                    | 5.6                       | 6.3                        | 331               | 31.4                     |

| 11                    | 90.7                      | 93.5                       | 1.26              | 8230                     | 36                    | 5.0                       | 5.7                        | 415               | 25.0                     |

| 12                    | 80.8                      | 83.3                       | 1.59              | 6530                     | 37                    | 4.5                       | 5.1                        | 512               | 20.2                     |

| 13                    | 72.0                      | 74.1                       | 2.00              | 5180                     | 38                    | 4.0                       | 4.5                        | 648               | 16.0                     |

| 14                    | 64.1                      | 66.7                       | 2.52              | 4110                     | 39                    | 3.5                       | 4.0                        | 847               | 12.2                     |

| 15                    | 57.1                      | 59.5                       | 3.18              | 3260                     | 40                    | 3.1                       | 3.5                        | 1080              | 9.61                     |

| 16                    | 50.8                      | 52.9                       | 4.02              | 2580                     | 41                    | 2.8                       | 3.1                        | 1320              | 7.84                     |

| 17                    | 45.3                      | 47.2                       | 5.05              | 2050                     | 42                    | 2.5                       | 2.8                        | 1660              | 6.25                     |

| 18                    | 40.3                      | 42.4                       | 6.39              | 1620                     | 43                    | 2.2                       | 2.5                        | 2140              | 4.84                     |

| 19                    | 35.9                      | 37.9                       | 8.05              | 1290                     | 44                    | 2.0                       | 2.3                        | 2590              | 4.00                     |

| 20                    | 32.0                      | 34.0                       | 10.1              | 1020                     | 45                    | 1.76                      | 1.9                        | 3350              | 3.10                     |

| 21                    | 28.5                      | 30.2                       | 12.8              | 812                      | 46                    | 1.57                      | 1.7                        | 4210              | 2.46                     |

| 22                    | 25.3                      | 27.0                       | 16.2              | 640                      | 47                    | 1.40                      | 1.6                        | 5290              | 1.96                     |

| 23                    | 22.6                      | 24.2                       | 20.3              | 511                      | 48                    | 1.24                      | 1.4                        | 6750              | 1.54                     |

| 24                    | 20.1                      | 21.6                       | 25.7              | 404                      | 49                    | 1.11                      | 1.3                        | 8420              | 1.23                     |

| 25                    | 17.9                      | 19.3                       | 32.4              | 320                      | 50                    | .99                       | 1.1                        | 10600             | 0.98                     |

<sup>\* 1</sup> mil =  $2.54 \times 10^{-3}$  cm

TABLE 1-1. AWG Wire Chart

Keep in mind that even though optimum Q is attained when the length of the coil (l) is equal to its diameter (2r), this is sometimes not practical and, in many cases, the length is much greater than the diameter. In Example 1-5, we calculated the need for 4.8 turns of wire in a length of 0.635 cm and decided that No. 18 AWG wire would fit. The only problem with this approach is that when the design is finished, we end up with a very tightly wound coil. This increases the distributed capacitance between the turns and, thus, lowers the useful frequency range of the inductor by lowering its resonant frequency. We could take either one of the following compromise solutions to this dilemma:

**1.** Use the next smallest AWG wire size to wind the inductor while keeping the length (*l*) the same. This approach will allow a small air gap between windings and, thus,

- decrease the interwinding capacitance. It also, however, increases the resistance of the windings by decreasing the diameter of the conductor and, thus, it lowers the Q.

- 2. Extend the length of the inductor (while retaining the use of No. 18 AWG wire) just enough to leave a small air gap between the windings. This method will produce the same effect as Method No. 1. It reduces the *Q* somewhat but it decreases the interwinding capacitance considerably.

#### **Magnetic-Core Materials**

In many RF applications, where large values of inductance are needed in small areas, air-core inductors cannot be used because of their size. One method of decreasing the size of a coil

while maintaining a given inductance is to decrease the number of turns while at the same time increasing its magnetic flux density. The flux density can be increased by decreasing the "reluctance" or magnetic resistance path that links the windings of the inductor. We do this by adding a magnetic-core material, such as iron or ferrite, to the inductor. The permeability  $(\mu)$  of this material is much greater than that of air and, thus, the magnetic flux isn't as "reluctant" to flow between the windings. The net result of adding a high permeability core to an inductor is the gaining of the capability to wind a given inductance with fewer turns than what would be required for an air-core inductor. Thus, several advantages can be realized.

- Smaller size—due to the fewer number of turns needed for a given inductance.

- **2.** Increased *Q*—fewer turns means less wire resistance.

- **3.** Variability—obtained by moving the magnetic core in and out of the windings.

There are some major problems that are introduced by the use of magnetic cores, however, and care must be taken to ensure that the core that is chosen is the right one for the job. Some of the problems are:

- 1. Each core tends to introduce its own losses. Thus, adding a magnetic core to an air-core inductor could possibly *decrease* the *Q* of the inductor, depending on the material used and the frequency of operation.

- 2. The permeability of all magnetic cores changes with frequency and usually decreases to a very small value at the upper end of their operating range. It eventually approaches the permeability of air and becomes "invisible" to the circuit.

- The higher the permeability of the core, the more sensitive it is to temperature variation. Thus, over wide temperature ranges, the inductance of the coil may vary appreciably.

- **4.** The permeability of the magnetic core changes with applied signal level. If too large an excitation is applied, saturation of the core will result.

These problems can be overcome if care is taken, in the design process, to choose cores wisely. Manufacturers now supply excellent literature on available sizes and types of cores, complete with their important characteristics.

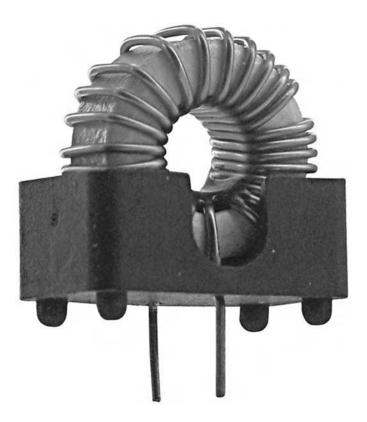

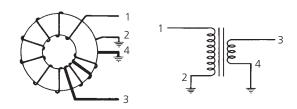

#### **TOROIDS**

A toroid, very simply, is a ring or doughnut-shaped magnetic material that is widely used to wind RF inductors and transformers. Toroids are usually made of iron or ferrite. They come in various shapes and sizes (Fig. 1-20) with widely varying characteristics. When used as cores for inductors, they can typically yield very high *Q*s. They are self-shielding, compact, and best of all, easy to use.

FIG. 1-20. Toroidal core inductor. (Courtesy of Allied Electronics)

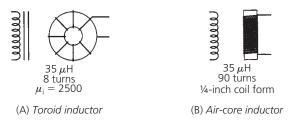

The Q of a toroidal inductor is typically high because the toroid can be made with an extremely high permeability. As was discussed in an earlier section, high permeability cores allow the designer to construct an inductor with a given inductance (for example, 35  $\mu$ H) with fewer turns than is possible with an aircore design. Fig. 1-21 indicates the potential savings obtained in number of turns of wire when coil design is changed from aircore to toroidal-core inductors. The air-core inductor, if wound for optimum Q, would take 90 turns of a very small wire (in order to fit all turns within a 1/4-inch length) to reach 35  $\mu$ H; however, the toroidal inductor would only need 8 turns to reach the design goal. Obviously, this is an extreme case but it serves a useful purpose and illustrates the point. The toroidal core does require fewer turns for a given inductance than does an air-core design. Thus, there is less AC resistance and the Q can be increased dramatically.

FIG. 1-21. Turns comparison between inductors for the same inductance.

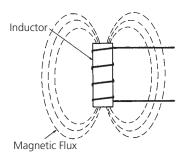

The self-shielding properties of a toroid become evident when Fig. 1-22 is examined. In a typical aircore inductor, the magnetic-flux lines linking the turns of the inductor take the shape shown in Fig. 1-22A. The sketch clearly indicates that the air surrounding the inductor is definitely part of the magnetic-flux path. Thus, this inductor tends to radiate the RF signals flowing within. A toroid, on the other hand (Fig. 1-22B), completely contains the magnetic flux within the material itself; thus, no radiation occurs. In actual practice, of course, some radiation will occur but it is minimized. This characteristic of toroids eliminates the need for bulky shields surrounding the inductor. The shields not only tend to reduce available space, but they also reduce the *Q* of the inductor that they are shielding.

(A) Typical inductor

FIG. 1-22. Shielding effect of a toroidal inductor.

#### Core Characteristics

Earlier, we discussed, in general terms, the relative advantages and disadvantages of using magnetic cores. The following discussion of typical toroidal-core characteristics will aid you in specifying the core that you need for your particular application.

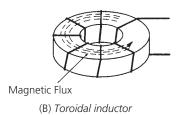

Fig. 1-23 is a typical magnetization curve for a magnetic core. The curve simply indicates the magnetic-flux density (B) that occurs in the inductor with a specific magnetic-field intensity (H) applied. As the magnetic-field intensity is increased from zero (by increasing the applied signal voltage), the magnetic-flux density that links the turns of the inductor increases quite linearly. The ratio of the magnetic-flux density to the magnetic-field intensity is called the permeability of the material. This has already been mentioned on numerous occasions.

$$\mu = B/H$$

(webers/ampere-turn) (Eq. 1-9)

Thus, the permeability of a material is simply a measure of how well it transforms an electrical excitation into a magnetic

FIG. 1-23. Magnetization curve for a typical core.

flux. The better it is at this transformation, the higher is its permeability.

As mentioned previously, initially the magnetization curve is linear. It is during this linear portion of the curve that permeability is usually specified and, thus, it is sometimes called initial permeability ( $\mu_i$ ) in various core literature. As the electrical excitation increases, however, a point is reached at which the magnetic-flux intensity does not continue to increase at the same rate as the excitation and the slope of the curve begins to decrease. Any further increase in excitation may cause *saturation* to occur.  $H_{\text{sat}}$  is the excitation point above which no further increase in magnetic-flux density occurs ( $B_{\text{sat}}$ ). The incremental permeability above this point is the same as air. Typically, in RF circuit applications, we keep the excitation small enough to maintain linear operation.

$B_{\rm sat}$  varies substantially from core to core, depending upon the size and shape of the material. Thus, it is necessary to read and understand the manufacturer's literature that describes the particular core you are using. Once  $B_{\rm sat}$  is known for the core, it is a very simple matter to determine whether or not its use in a particular circuit application will cause it to saturate. The in-circuit operational flux density  $(B_{\rm op})$  of the core is given by the formula:

$$B_{\rm op} = \frac{E \times 10^8}{(4.44) f \, NA_e}$$

(Eq. 1-10)

where,

$B_{\rm op}$  = the magnetic-flux density in gauss,

E = the maximum rms voltage across the inductor in volts,

f = the frequency in hertz,

N = the number of turns,

$A_e$  = the effective cross-sectional area of the core in cm<sup>2</sup>.

Toroids

Thus, if the calculated  $B_{\rm op}$  for a particular application is less than the published specification for  $B_{\rm sat}$ , then the core will not saturate and its operation will be somewhat linear.

Another characteristic of magnetic cores that is very important to understand is that of internal loss. It has previously been mentioned that the careless addition of a magnetic core to an air-core inductor could possibly *reduce* the *Q* of the inductor. This concept might seem contrary to what we have studied so far, so let's examine it a bit more closely.

The equivalent circuit of an air-core inductor (Fig. 1-15) is reproduced in Fig. 1-24A for your convenience. The Q of this inductor is

$$Q = \frac{X_L}{R_s}$$

(Eq. 1-11)

where

$X_L = \omega L$ ,

$R_s$  = the resistance of the windings.

FIG. 1-24. Equivalent circuits for air-core and magnetic-core inductors.

If we add a magnetic core to the inductor, the equivalent circuit becomes like that shown in Fig. 1-24B. We have added resistance  $R_p$  to represent the losses which take place in the core itself. These losses are in the form of hysteresis. Hysteresis is the power lost in the core due to the realignment of the magnetic particles within the material with changes in excitation, and the eddy currents that flow in the core due to the voltages induced within. These two types of internal loss, which are inherent to some degree in every magnetic core and are thus unavoidable, combine to reduce the efficiency of the inductor and, thus, increase its loss. But what about the new Q for the magnetic-core inductor? This question isn't as easily answered. Remember, when a magnetic core is inserted into an existing inductor, the value of the inductance is increased. Therefore, at any given frequency, its reactance increases proportionally. The question that must be answered then, in order to determine the new Q of the inductor, is: By what factors did the inductance and loss increase? Obviously, if by adding a toroidal core, the inductance were increased by a factor of two and its total loss was also increased by a factor of two, the Q would remain unchanged. If, however, the total coil loss were increased to four times its previous value while only doubling the inductance, the Q of the inductor would be reduced by a factor of two.

Now, as if all of this isn't confusing enough, we must also keep in mind that the additional loss introduced by the core is not constant, but varies (usually increases) with frequency. Therefore, the designer must have a complete set of manufacturer's data sheets for every core he is working with.

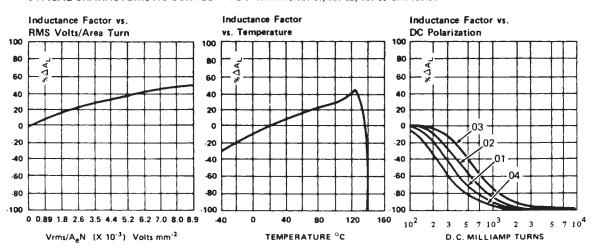

Toroid manufacturers typically publish data sheets which contain all the information needed to design inductors and transformers with a particular core. (Some typical specification and data sheets are given in Figs. 1-25 and 1-26.) In most cases, however, each manufacturer presents the information in a unique manner and care must be taken in order to extract the information that is needed without error, and in a form that can be used in the ensuing design process. This is not always as simple as it sounds. Later in this chapter, we will use the data presented in Figs. 1-25 and 1-26 to design a couple of toroidal inductors so that we may see some of those differences. Table 1-2 lists some of the commonly used terms along with their symbols and units.

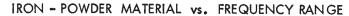

#### Powdered Iron vs. Ferrite

In general, there are no hard and fast rules governing the use of ferrite cores versus powdered-iron cores in RF circuit-design applications. In many instances, given the same permeability and type, either core could be used without much change in performance of the actual circuit. There are, however, special applications in which one core might outperform another, and it is those applications which we will address here.

Powdered-iron cores, for instance, can typically handle more RF power without saturation or damage than the same size ferrite core. For example, ferrite, if driven with a large amount of RF power, tends to retain its magnetism permanently. This ruins the core by changing its permeability permanently. Powdered iron, on the other hand, if overdriven will eventually return to its initial permeability ( $\mu_i$ ). Thus, in any application where high RF power levels are involved, iron cores might seem to be the best choice.

In general, powdered-iron cores tend to yield higher-Q inductors, at higher frequencies, than an equivalent size ferrite core. This is due to the inherent core characteristics of powdered iron cores which produce much less internal loss than ferrite cores. This characteristic of powdered iron makes it very useful in narrowband or tuned-circuit applications. Table 1-3 lists a few of the common powdered-iron core materials along with their typical applications.

At very low frequencies, or in broadband circuits which span the spectrum from VLF up through VHF, ferrite seems to be the general choice. This is true because, for a given core size, ferrite cores have a much higher permeability. The higher permeability is needed at the low end of the frequency range where, for a given inductance, fewer windings would be needed with the ferrite core. This brings up another point. Since ferrite cores, in general, have a higher permeability than the same size powdered-iron core, a coil of a given inductance can usually be wound on a much smaller ferrite core and with fewer turns. Thus, we can save circuit board area.

#### **BROAD BAND-RATED FERRAMIC COMPONENTS**

- Values measured at 100 KHz, T = 25°C.

- Temperature Coefficient (TC) = 0 to +0.75% / $^{\circ}$ C max., -40 to +70 $^{\circ}$ C.

Nom.  $\mu_i$  2500

- Disaccommodation (D) = 3.0% max., 10-100 min., 25°C.

- Hysteresis Core Constant  $(\eta_i)$  measured at 20 KHz to 30 gauss (3 milli Tesla).

- For mm dimensions and core constants, see page 30.

#### MECHANICAL SPECIFICATIONS

|                | F     | PART N | UMBER | 3     |         |       |

|----------------|-------|--------|-------|-------|---------|-------|

|                | AA-01 | AA-02  | AA-03 | AA-04 | TOL     | UNITS |

| d <sub>1</sub> | 0.135 | 0.155  | 0.230 | 0.100 | ± 0.005 | in.   |

| d <sub>2</sub> | 0.065 | 0.088  | 0.120 | 0.050 | ± 0.005 | in.   |

| h              | 0.055 | 0.051  | 0.060 | 0.050 | ± 0.005 | in.   |

#### **ELECTRICAL SPECIFICATIONS**

|                       | [     | PART N |       |       |       |                       |

|-----------------------|-------|--------|-------|-------|-------|-----------------------|

|                       | AA-01 | AA-02  | AA-03 | AA-04 | TOL   | UNITS                 |

| AL                    | 510   | 365    | 495   | 440   | ± 20% | nH/turn <sup>2</sup>  |

| $X_p/N^2$             | 0.320 | 0.229  | 0.310 | 0.276 | ± 20% | ohm/turn <sup>2</sup> |

| $R_p/N^2$             | 10.4  | 7.5    | 10.0  | 8.9   | min.  | ohm/turn <sup>2</sup> |

| Q.                    | 54    | 54     | 54    | 54    | min.  |                       |

| V <sub>ms</sub>       | 7.9   | 7.1    | 13.6  | 5.1   | max.  | mv                    |

| $\eta_{\mathfrak{i}}$ | 1,480 | 1,400  | 0,920 | 2,150 | max.  | VSA-2 H-3/2           |

#### TYPICAL CHARACTERISTIC CURVES - Part Numbers: AA-01, AA-02, AA-03 and AA-04

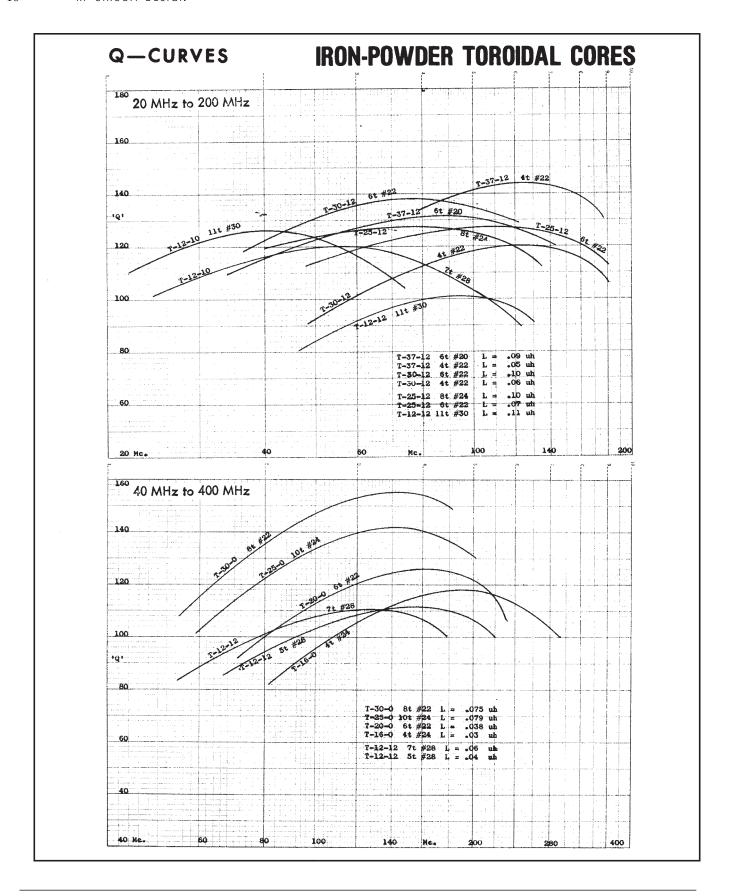

## **IRON-POWDER TOROIDAL CORES**

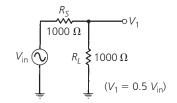

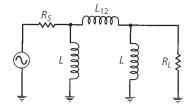

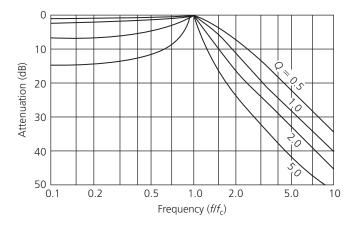

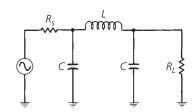

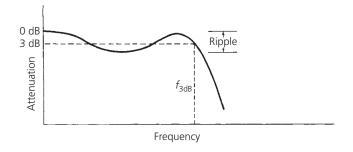

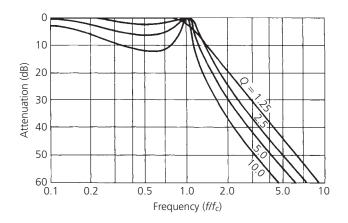

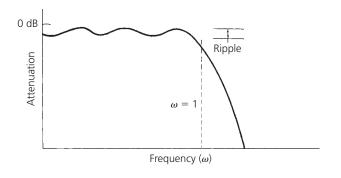

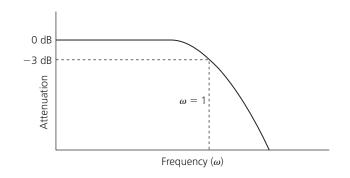

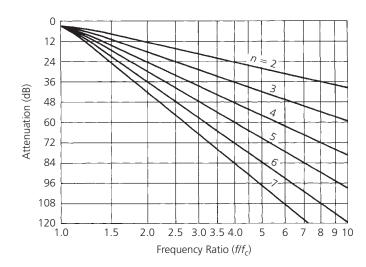

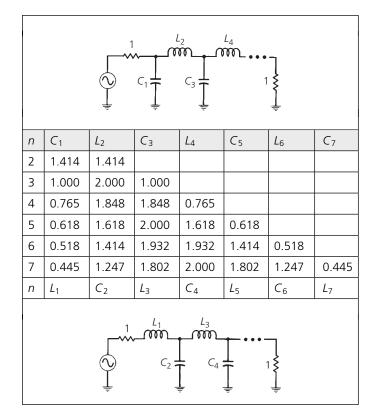

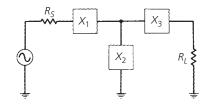

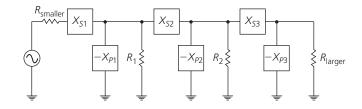

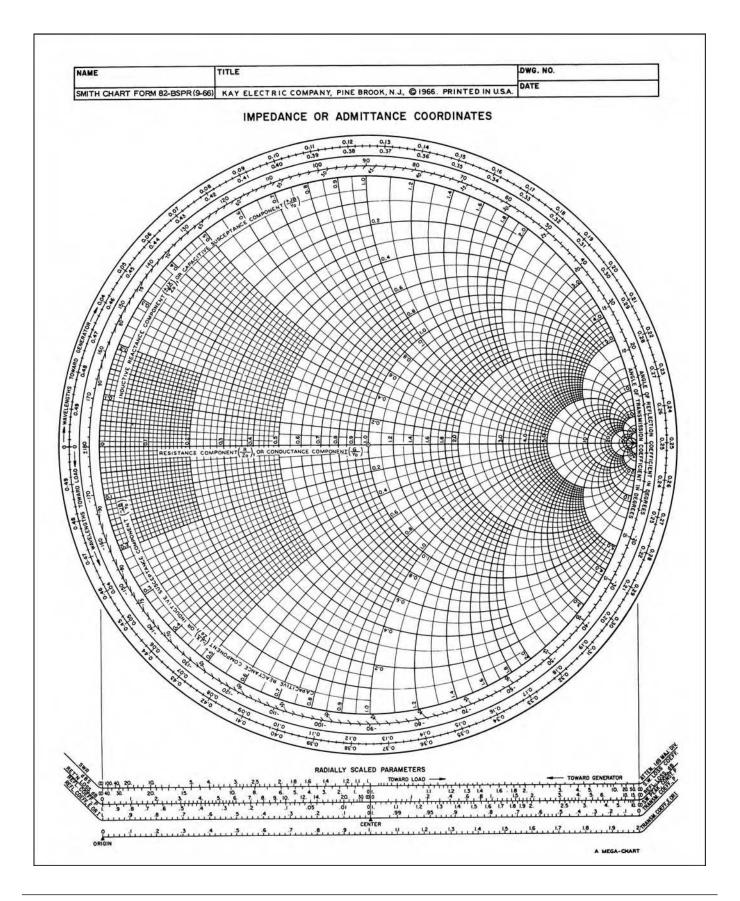

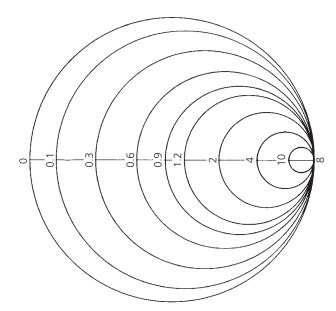

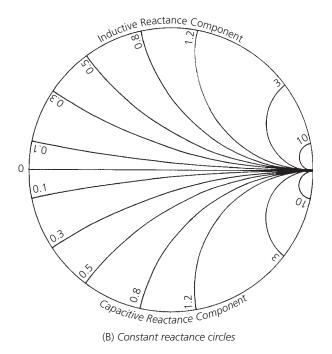

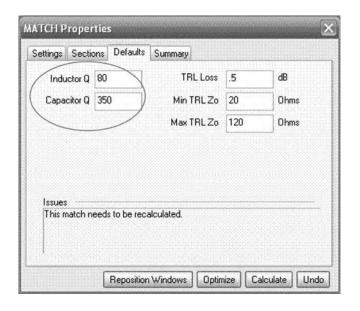

|                |                        | PHY                    | SICAL DIMENSI  | ons                                      |                        |